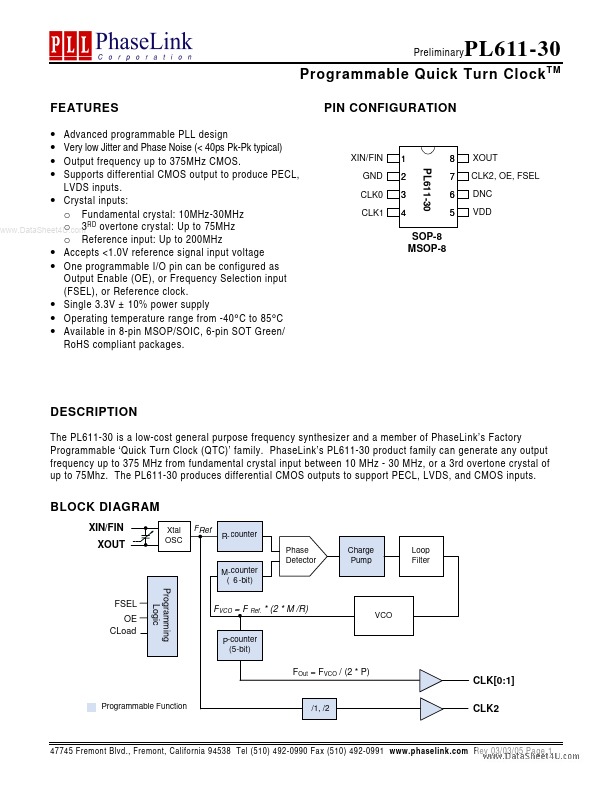

PL611-30 Overview

The PL611-30 is a low-cost general purpose frequency synthesizer and a member of PhaseLink’s Factory Programmable ‘Quick Turn Clock (QTC)’ family. PhaseLink’s PL611-30 product family can generate any output frequency up to 375 MHz from fundamental crystal input between 10 MHz - 30 MHz, or a 3rd overtone crystal of up to 75Mhz. The PL611-30 produces differential CMOS outputs to support PECL, LVDS, and CMOS inputs.

PL611-30 Key Features

- Crystal inputs: o Fundamental crystal: 10MHz-30MHz o 3 RD overtone crystal: Up to 75MHz .. o Reference input: Up to 200M

- Accepts <1.0V reference signal input voltage

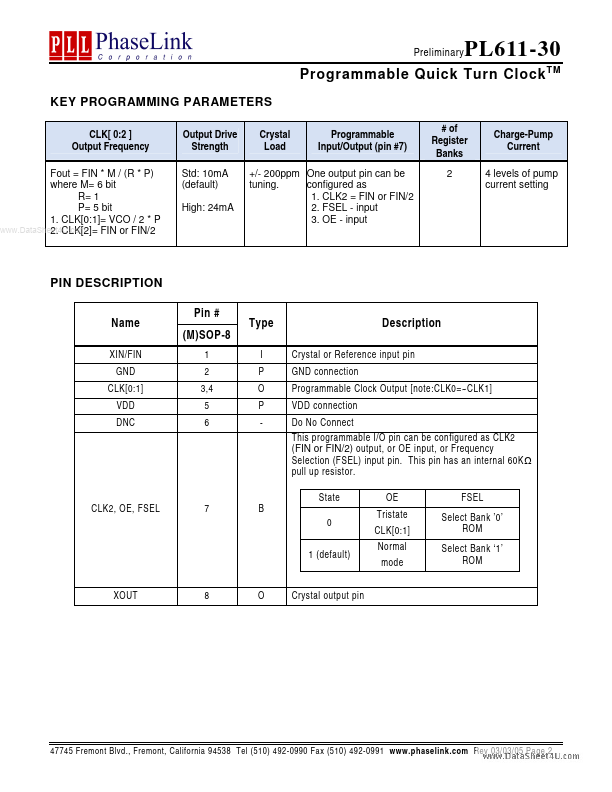

- One programmable I/O pin can be configured as Output Enable (OE), or Frequency Selection input (FSEL), or Reference cloc

- Single 3.3V ± 10% power supply

- Operating temperature range from -40 ° C to 85 ° C

- Available in 8-pin MSOP/SOIC, 6-pin SOT Green/ RoHS pliant packages