PLL620-06

PLL620-06 is Low Phase Noise XO manufactured by PhaseLink.

- Part of the PLL620-05 comparator family.

- Part of the PLL620-05 comparator family.

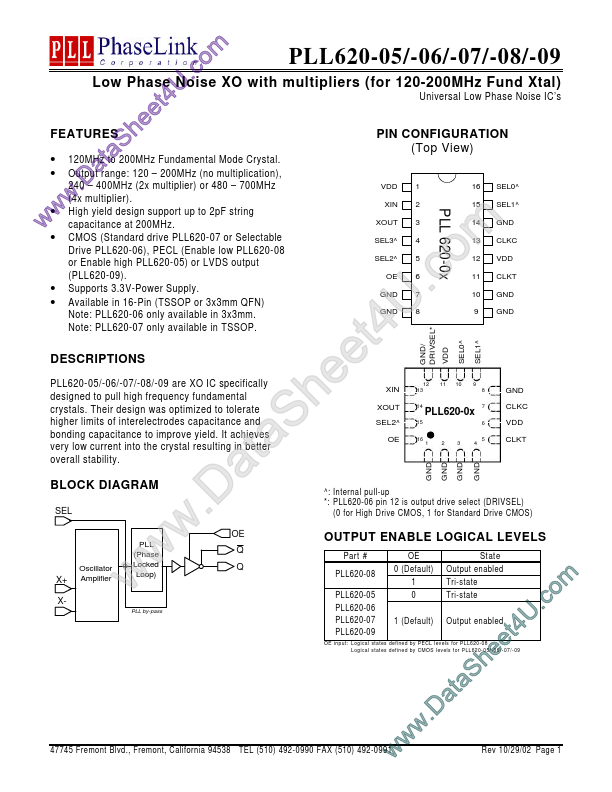

FEATURES h PIN CONFIGURATION S (Top View) a200MHz Fundamental Mode Crystal.

- 120MHz to t

- Output a range: 120

- 200MHz (no multiplication), D 240

- 400MHz (2x multiplier) or 480

- 700MHz . (4x multiplier). w

- w High yield design support up to 2p F string at 200MHz. w- capacitance CMOS (Standard drive PLL620-07 or Selectable

VDD 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 SEL0^ SEL1^ GND XIN

- -

GND/ DRIVSEL-

Drive PLL620-06), PECL (Enable low PLL620-08 or Enable high PLL620-05) or LVDS output (PLL620-09). Supports 3.3V-Power Supply. Available in 16-Pin (TSSOP or 3x3mm QFN) Note: PLL620-06 only available in 3x3mm. Note: PLL620-07 only available in TSSOP.

DESCRIPTIONS

BLOCK DIAGRAM

^: Internal pull-up

- : PLL620-06 pin 12 is output drive select (DRIVSEL) (0 for High Drive CMOS, 1 for Standard Drive CMOS)

OE Q Q

X+ X-

Oscillator Amplifier

PLL (Phase Locked Loop)

OUTPUT ENABLE LOGICAL LEVELS

Part # PLL620-08 PLL620-05 PLL620-06 PLL620-07 PLL620-09

PLL by-pass

OE input: Logical states defined by PECL levels for PLL620-08 Logical states defined by CMOS levels for PLL620-05/-06/-07/-09

47745 Fremont Blvd., Fremont, California 94538 TEL (510) 492-0990 FAX (510) 492-0991 m o .c U 4 t e e h S a at .D w w w

1 (Default) Output enabled Rev 10/29/02 Page 1

OE 0 (Default) 1 0

State Output enabled Tri-state Tri-state

PLL620-05/-06/-07/-08/-09 are XO IC specifically designed to pull high frequency fundamental crystals. Their design was optimized to tolerate higher limits of interelectrodes capacitance and bonding capacitance to improve yield. It achieves very low current into the crystal resulting in better overall stability. m o .c U 4 t e e h S a t a .D w w w

XOUT SEL3^ SEL2^ OE GND GND

SEL0^

SEL1^

PLL 620-0x

CLKC VDD CLKT GND...