Datasheet Summary

Features

- -

- - w-

- -

- -

- - w w

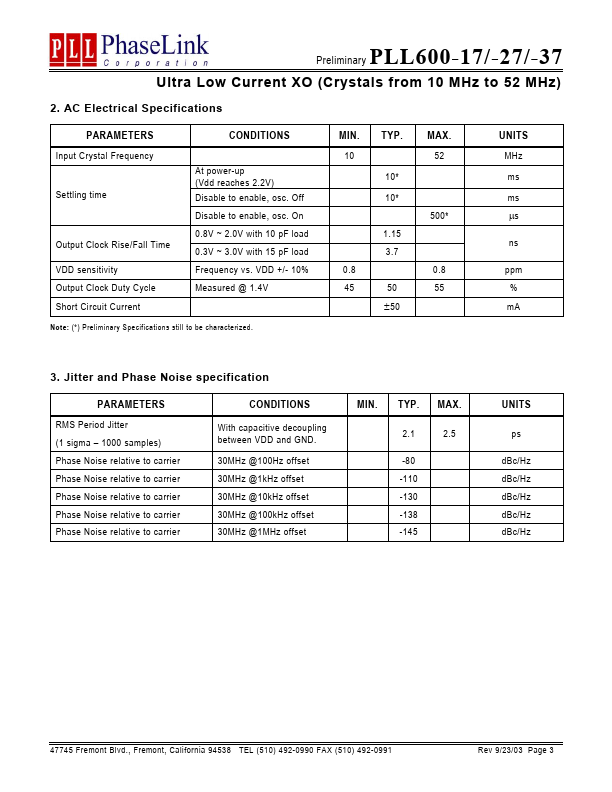

Low phase noise (-130 dBc @ 10kHz offset). CMOS output with OE tri-state control. Selectable oscillator “on” or “off” feature in output disable mode Ultra Low current consumption (<2.5mA, <2mA, <1.3mA at 27MHz respectively for PLL600-17, PLL600-27, and PLL600-37) Ultra Low disable mode current (<2uA when disabled with osc. off) 10 to 52MHz fundamental crystal input. Selectable divider by 2 (PLL600-17 only). 12mA drive capability at TTL output. Low jitter (RMS): 2.5ps period jitter. 2.25V to 3.63V DC operation. Available in 8 pin SOIC, 6 pin SOT or DIE.

.D at h S a t e e

Ultra Low Current XO (Crystals from 10 MHz to 52 MHz)

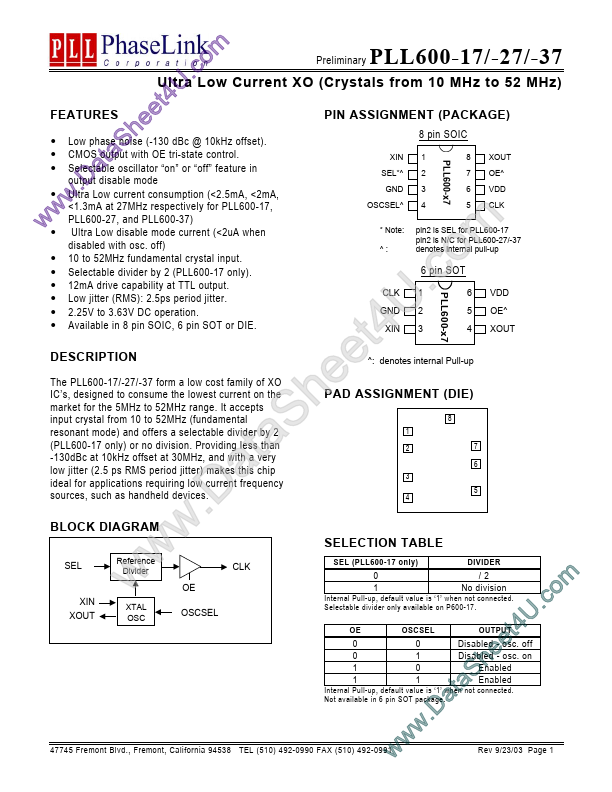

PIN ASSIGNMENT...