PI4MSD5V9547 Overview

Key Specifications

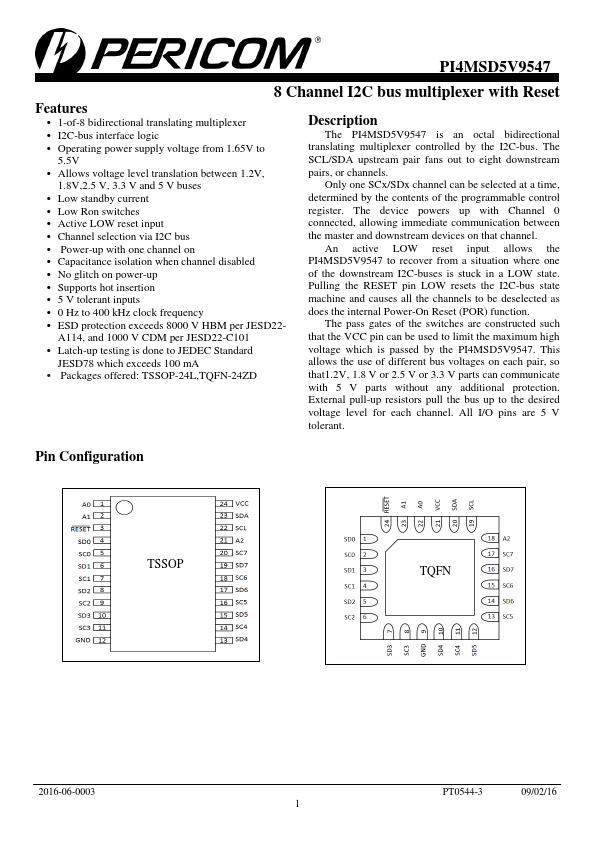

Package: TSSOP

Operating Voltage: 3.6 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 1.65 V

Description

The PI4MSD5V9547 is an octal bidirectional translating multiplexer controlled by the I2C-bus. The SCL/SDA upstream pair fans out to eight downstream pairs, or channels.