| Part | PE42850 |

|---|---|

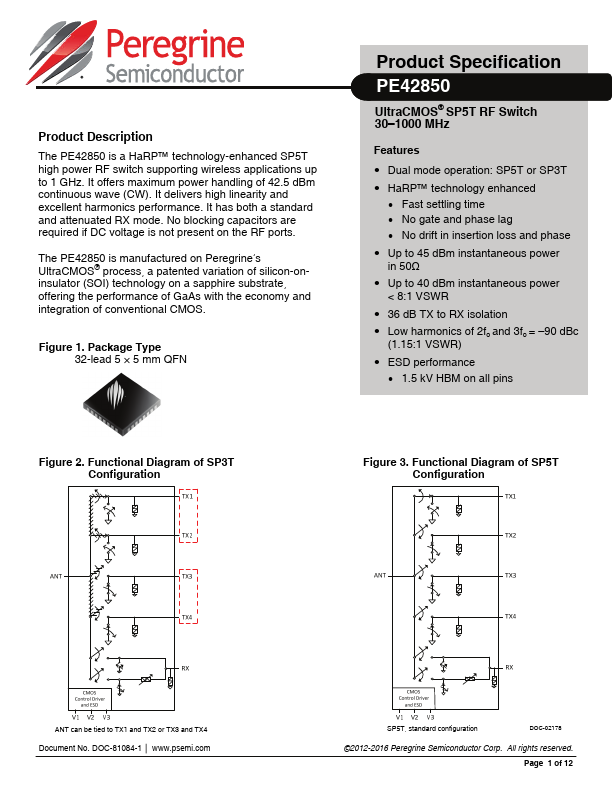

| Description | UltraCMOS SP5T RF Switch |

| Manufacturer | pSemi |

| Size | 509.07 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| SW-331 | Tyco Electronics | Matched GaAs SPDT Switch |

| B3045G | onsemi | Switch-mode Power Rectifiers |

| DK1203 | Dongke Semiconductor | AC-DC Switch Mode Power controller |