PCS3P623Z05B

Description

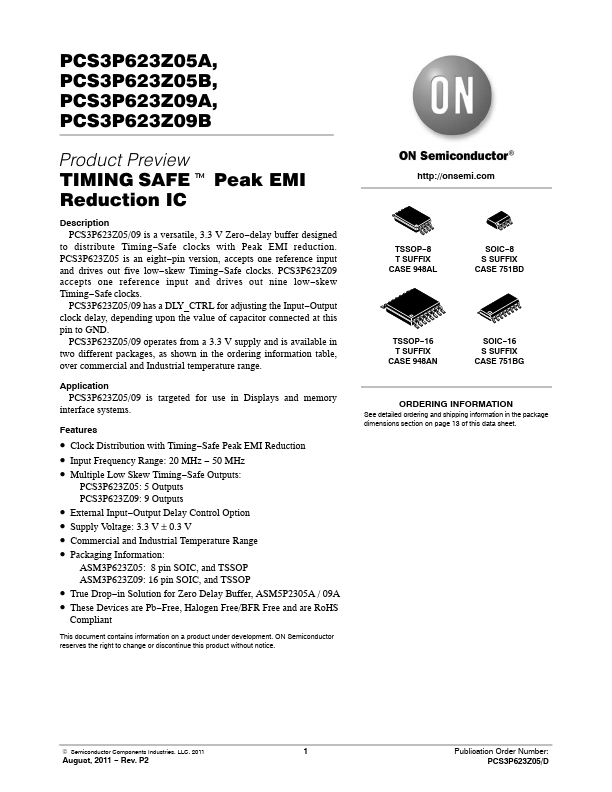

PCS3P623Z05/09 is a versatile, 3.3 V Zero-delay buffer designed to distribute Timing-Safe clocks with Peak EMI reduction.

Key Features

- Clock Distribution with Timing-Safe Peak EMI Reduction

- Input Frequency Range: 20 MHz - 50 MHz

- External Input-Output Delay Control Option

- Supply Voltage: 3.3 V ± 0.3 V

- mercial and Industrial Temperature Range

- True Drop-in Solution for Zero Delay Buffer, ASM5P2305A / 09A