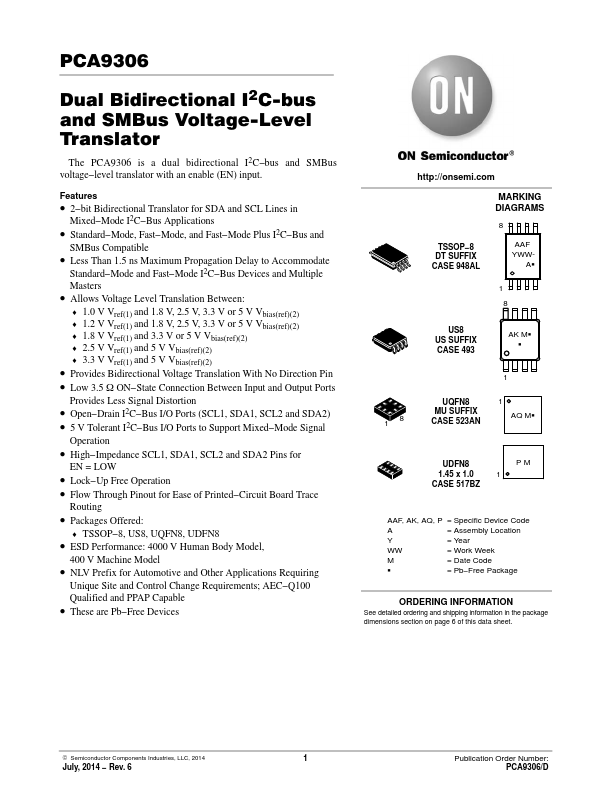

PCA9306

Key Features

- 2-bit Bidirectional Translator for SDA and SCL Lines in Mixed-Mode I2C-Bus Applications

- Standard-Mode, Fast-Mode, and Fast-Mode Plus I2C-Bus and SMBus Compatible

- Less Than 1.5 ns Maximum Propagation Delay to Accommodate Standard-Mode and Fast-Mode I2C-Bus Devices and Multiple Masters

- Allows Voltage Level Translation Between:

- 1.0 V Vref(1) and 1.8 V, 2.5 V, 3.3 V or 5 V Vbias(ref)(2)

- 1.2 V Vref(1) and 1.8 V, 2.5 V, 3.3 V or 5 V Vbias(ref)(2)

- 1.8 V Vref(1) and 3.3 V or 5 V Vbias(ref)(2)

- 2.5 V Vref(1) and 5 V Vbias(ref)(2)

- 3.3 V Vref(1) and 5 V Vbias(ref)(2)

- Provides Bidirectional Voltage Translation With No Direction Pin