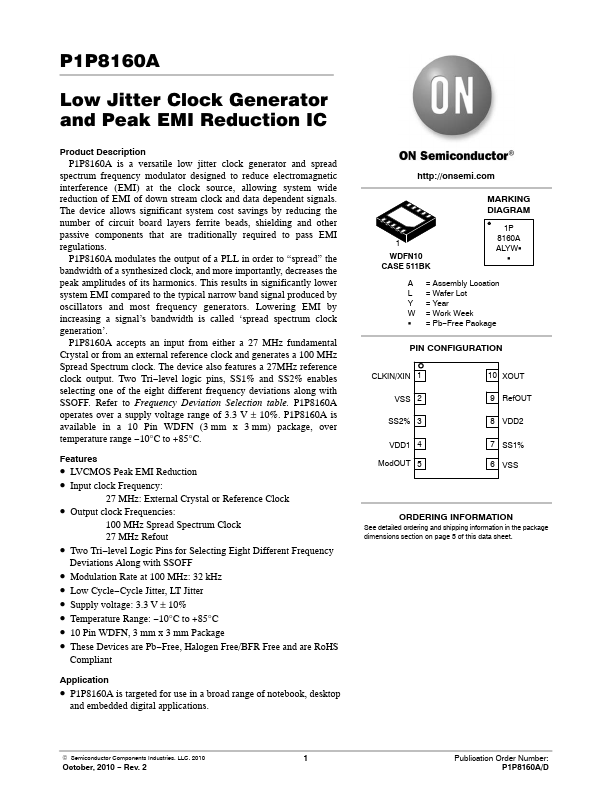

P1P8160A

P1P8160A is Low Jitter Clock Generator and Peak EMI Reduction IC manufactured by onsemi.

Low Jitter Clock Generator and Peak EMI Reduction IC

Product Description P1P8160A is a versatile low jitter clock generator and spread spectrum frequency modulator designed to reduce electromagnetic interference (EMI) at the clock source, allowing system wide reduction of EMI of down stream clock and data dependent signals. The device allows significant system cost savings by reducing the number of circuit board layers ferrite beads, shielding and other passive ponents that are traditionally required to pass EMI regulations.

P1P8160A modulates the output of a PLL in order to “spread” the bandwidth of a synthesized clock, and more importantly, decreases the peak amplitudes of...