NB7V58M

NB7V58M is 1.8 V / 2.5 V / 3.3 V Differential 2:1 Clock / Data Multiplexer / Translator manufactured by onsemi.

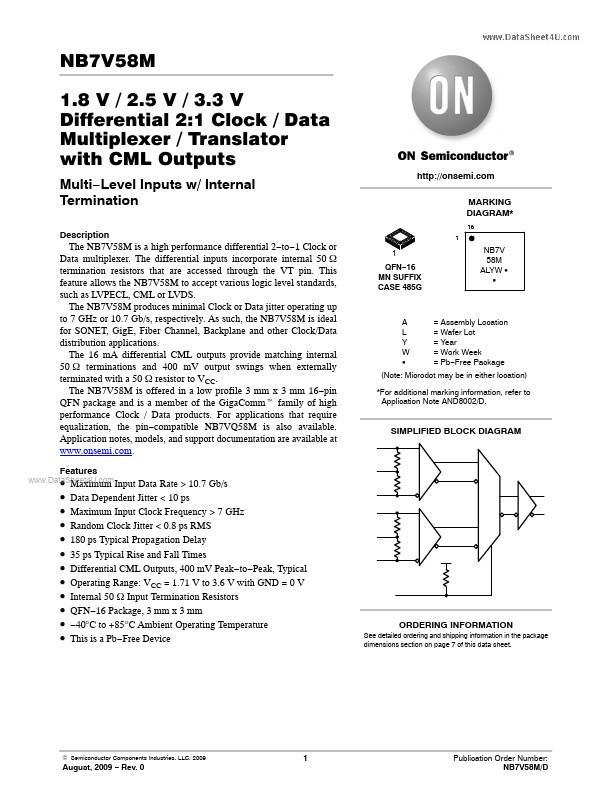

NB7V58M 1.8 V / 2.5 V / 3.3 V Differential 2:1 Clock / Data Multiplexer / Translator with CML Outputs

Multi- Level Inputs w/ Internal Termination

Description http://onsemi. MARKING DIAGRAM-

16 1

The NB7V58M is a high performance differential 2- to- 1 Clock or Data multiplexer. The differential inputs incorporate internal 50 W termination resistors that are accessed through the VT pin. This feature allows the NB7V58M to accept various logic level standards, such as LVPECL, CML or LVDS. The NB7V58M produces minimal Clock or Data jitter operating up to 7 GHz or 10.7 Gb/s, respectively. As such, the NB7V58M is ideal for SONET, GigE, Fiber Channel, Backplane and other Clock/Data distribution...