DS90UR124

Description

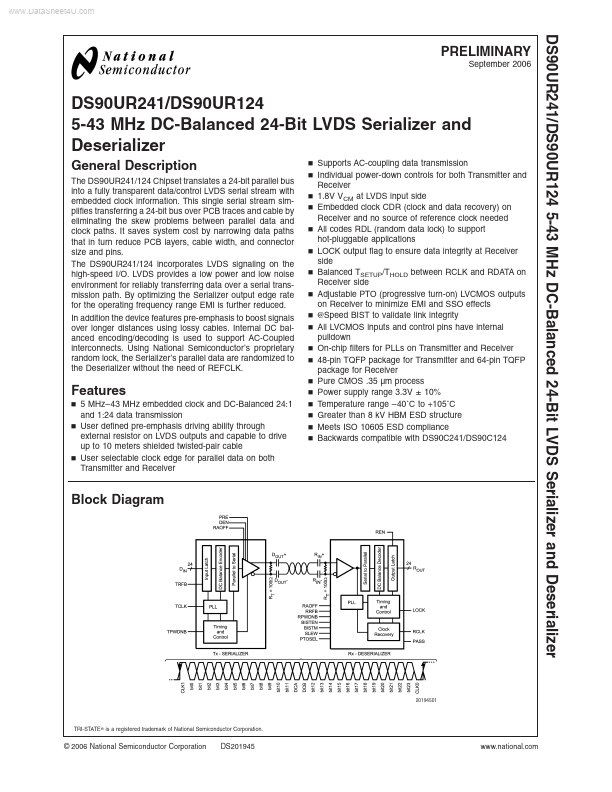

The DS90UR241/124 Chipset translates a 24-bit parallel bus into a fully transparent data/control LVDS serial stream with embedded clock information. This single serial stream simplifies transferring a 24-bit bus over PCB traces and cable by eliminating the skew problems between parallel data and clock paths.

Key Features

- User selectable clock edge for parallel data on both Transmitter and Receiver