DS32EL0124

Overview

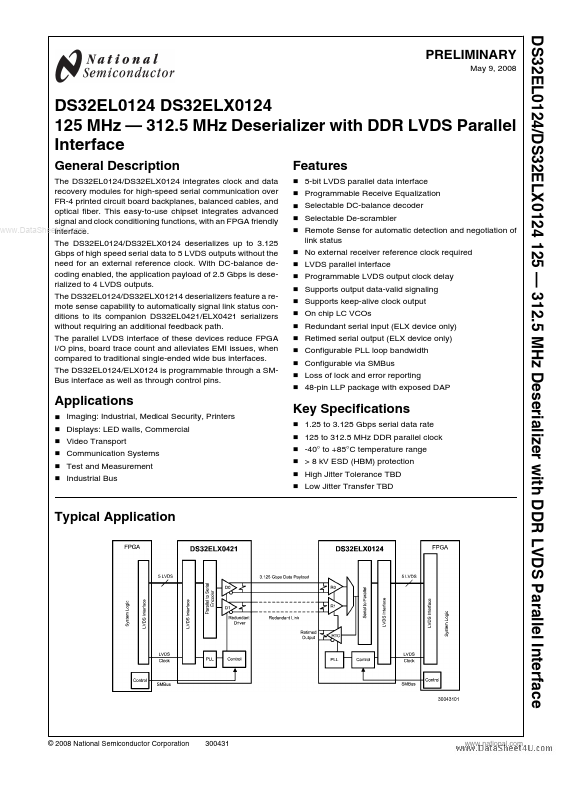

The DS32EL0124/DS32ELX0124 integrates clock and data recovery modules for high-speed serial communication over FR-4 printed circuit board backplanes, balanced cables, and optical fiber. This easy-to-use chipset integrates advanced signal and clock conditioning functions, with an FPGA friendly interface.

- 5-bit LVDS parallel data interface Programmable Receive Equalization Selectable DC-balance decoder Selectable De-scrambler Remote Sense for automatic detection and negotiation of link status No external receiver reference clock required LVDS parallel interface Programmable LVDS output clock delay Supports output data-valid signaling Supports keep-alive clock output On chip LC VCOs Redundant serial input (ELX device only) Retimed serial output (ELX device only) Configurable PLL loop bandwidth Configurable via SMBus Loss of lock and error reporting 48-pin LLP package with exposed DAP