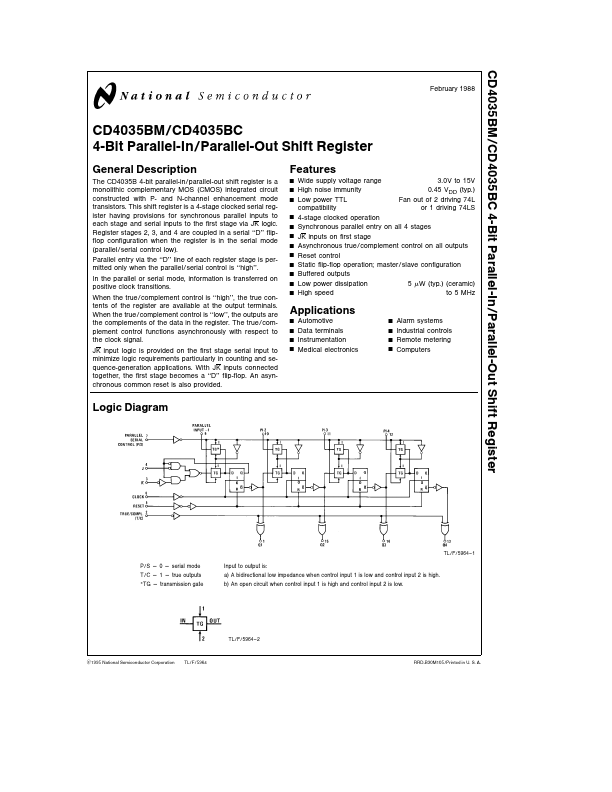

- Part: CD4035BM

- Description: 4-Bit Parallel-In/Parallel-Out Shift Register

- Manufacturer: National Semiconductor

- Size: 139.98 KB

Other CD4035BM Datasheets

| Manufacturer | Part Number | Description |

|---|---|---|

Texas Instruments

Texas Instruments |

CD4035BM | CMOS 4-STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER |

RCA

RCA |

CD4035B | CMOS 4-STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER |

Texas Instruments

Texas Instruments |

CD4035B | CMOS 4-STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER |

Texas Instruments

Texas Instruments |

CD4035BE | CMOS 4-STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER |

Texas Instruments

Texas Instruments |

CD4035BF | CMOS 4-STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER |