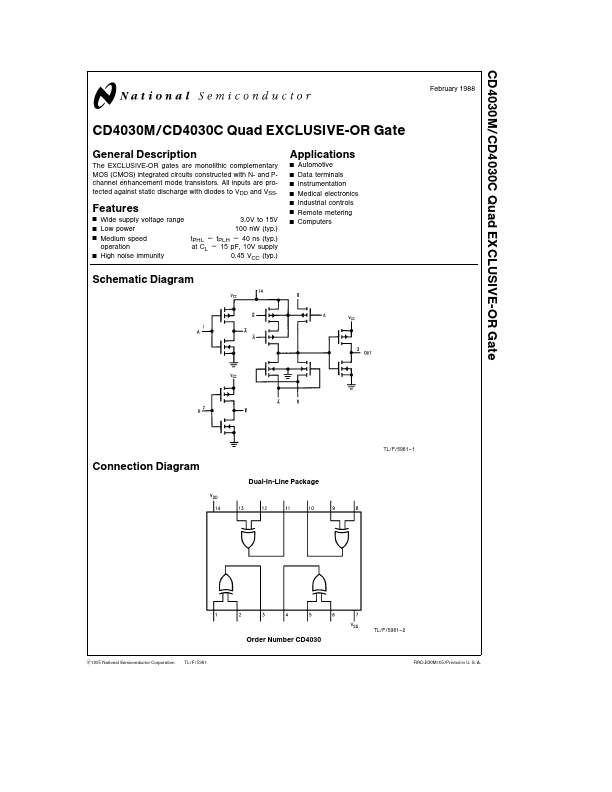

- Part: CD4030C

- Description: Quad EXCLUSIVE-OR Gate

- Manufacturer: National Semiconductor

- Size: 97.41 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| CD4030A | Harris Semiconductor | CMOS Quad Exclusive-OR Gate |

| CD4030A | RCA | CMOS Quad Exclusive-OR Gate |

| CD4030B | RCA | CMOS QUAD EXCLUSIVE-OR GATE |

| CD4030B | Texas Instruments | CMOS QUAD EXCLUSIVE-OR GATE |

| CD4030BF | Texas Instruments | CMOS QUAD EXCLUSIVE-OR GATE |

| CD4030BM | Texas Instruments | CMOS QUAD EXCLUSIVE-OR GATE |

| CD4036A | RCA Solid State | COS/MOS 4-Word by 8-Bit Random Access NDRO Memory |

| CD4035BE | Texas Instruments | CMOS 4-STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER |

| CD4035B | RCA | CMOS 4-STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER |

| CD4035BF | Texas Instruments | CMOS 4-STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER |