90CR283

90CR283 is DS90CR283 manufactured by National Semiconductor.

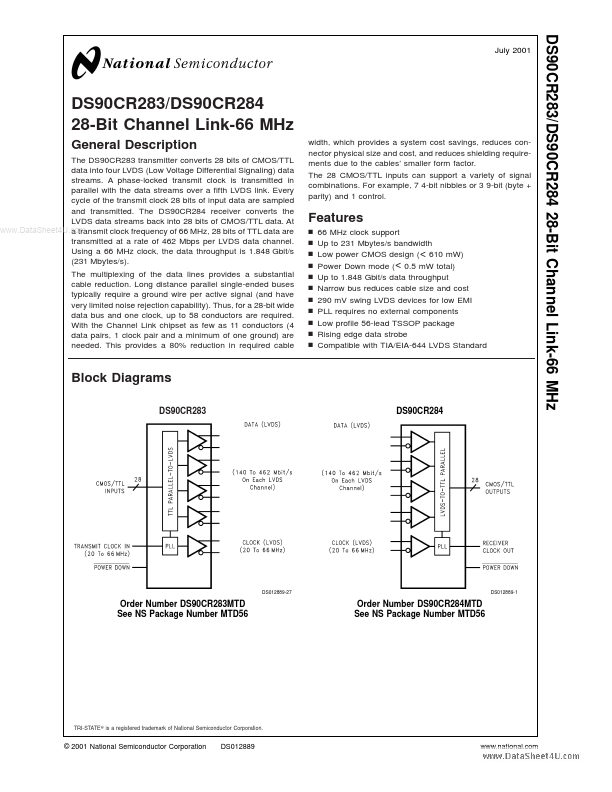

DS90CR283/DS90CR284 28-Bit Channel Link-66 MHz

July 2001

DS90CR283/DS90CR284 28-Bit Channel Link-66 MHz

General Description

The DS90CR283 transmitter converts 28 bits of CMOS/TTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. Every cycle of the transmit clock 28 bits of input data are sampled and transmitted. The DS90CR284 receiver converts the LVDS data streams back into 28 bits of CMOS/TTL data. At .. a transmit clock frequency of 66 MHz, 28 bits of TTL data are transmitted at a rate of 462 Mbps per LVDS data channel. Using a 66 MHz clock, the...