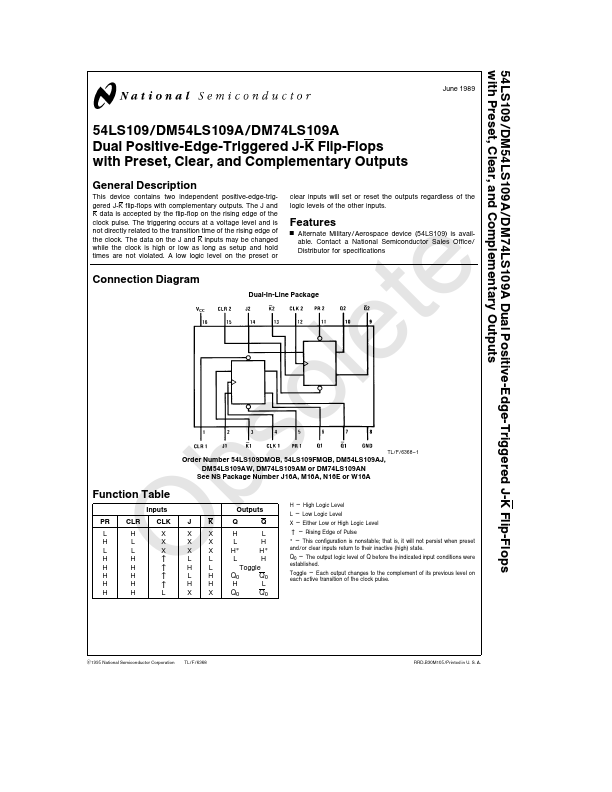

- Part: 54LS109

- Description: Dual Positive-Edge-Triggered J-K Flip-Flops

- Manufacturer: National Semiconductor

- Size: 330.29 KB

Other 54LS109 Datasheets

| Manufacturer | Part Number | Description |

|---|---|---|

Texas Instruments

Texas Instruments |

54LS109A | Dual J-K Positive-Edge-Triggered Flip-Flops |