NT5DS32M16DS Overview

Description

Nanya 512Mb SDRAMs is a high-speed CMOS Double Data Rate SDRAM containing 536,870,912 bits. It is internally configured as a qual-bank DRAM.

Key Features

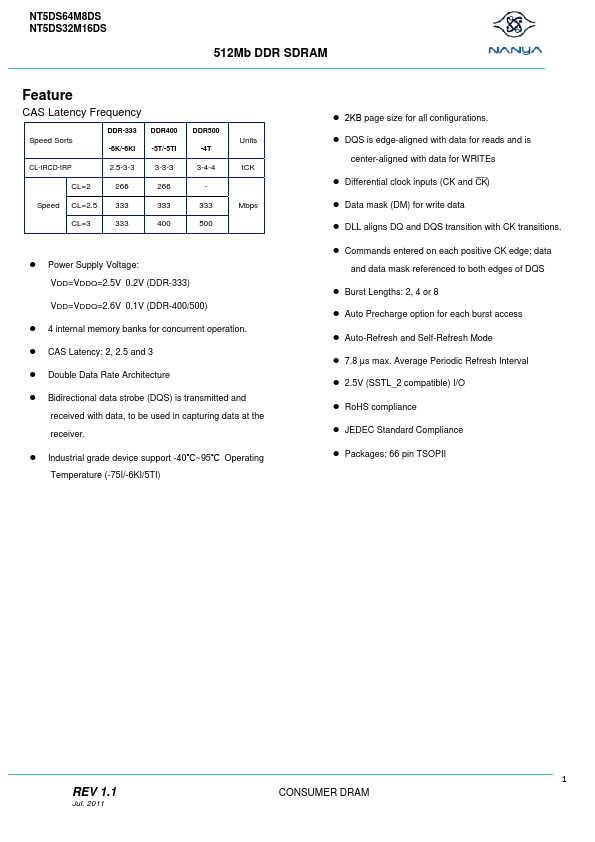

- 6K/-6KI CL-tRCD-tRP -4T

- Differential clock inputs (CK and CK) Mbps

- Data mask (DM) for write data

- DLL aligns DQ and DQS transition with CK transitions

- Commands entered on each positive CK edge; data

- Power Supply Voltage: VDD=VDDQ=2.5V 0.2V (DDR-333) VDD=VDDQ=2.6V 0.1V (DDR-400/500) and data mask referenced to both edges of DQS

- Burst Lengths: 2, 4 or 8

- Auto Precharge option for each burst access

- Auto-Refresh and Self-Refresh Mode z 7.8 µs max. Average Periodic Refresh Interval z 2.5V (SSTL_2 compatible) I/O

- RoHS compliance