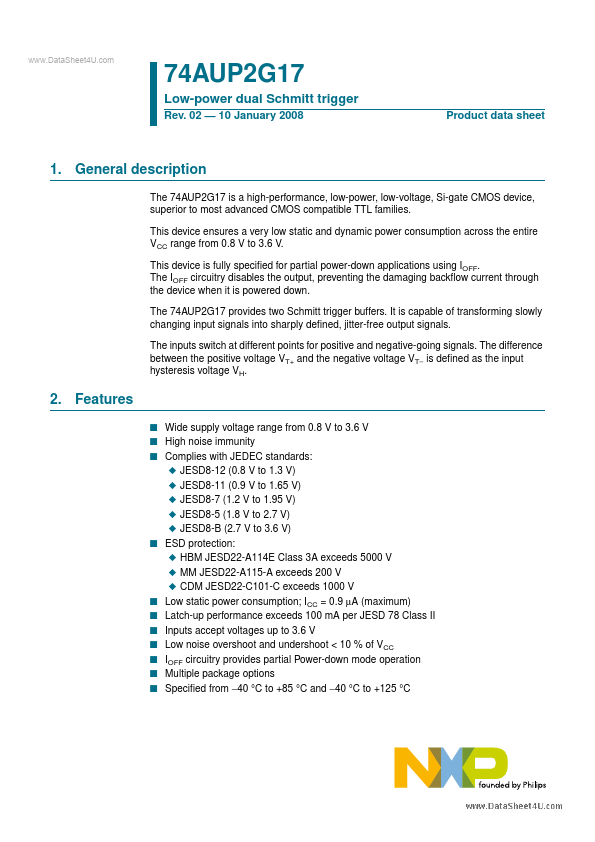

- Part: 74AUP2G17

- Description: Low-power dual Schmitt trigger

- Manufacturer: NXP Semiconductors

- Size: 137.94 KB

Datasheets by Manufacturer

- 74AUP2G17 — Diodes Incorporated — DUAL SCHMITT TRIGGER BUFFERS

- 74AUP2G126 — Diodes Incorporated — DUAL 3-STATE BUFFER

- 74AUP2G126 — NXP Semiconductors — Low-power dual buffer/line driver

- 74AUP2G14 — Diodes Incorporated — DUAL SCHMITT TRIGGER INVERTERS

- 74AUP2G157 — Nexperia — Low-power 2-input multiplexer

- 74AUP2G14 — Nexperia — Low-power dual Schmitt trigger inverter

- 74AUP2G125 — Nexperia — Low-power dual buffer/line driver

- 74AUP2G16 — Nexperia — Low-power dual buffer