TDA10025HN Overview

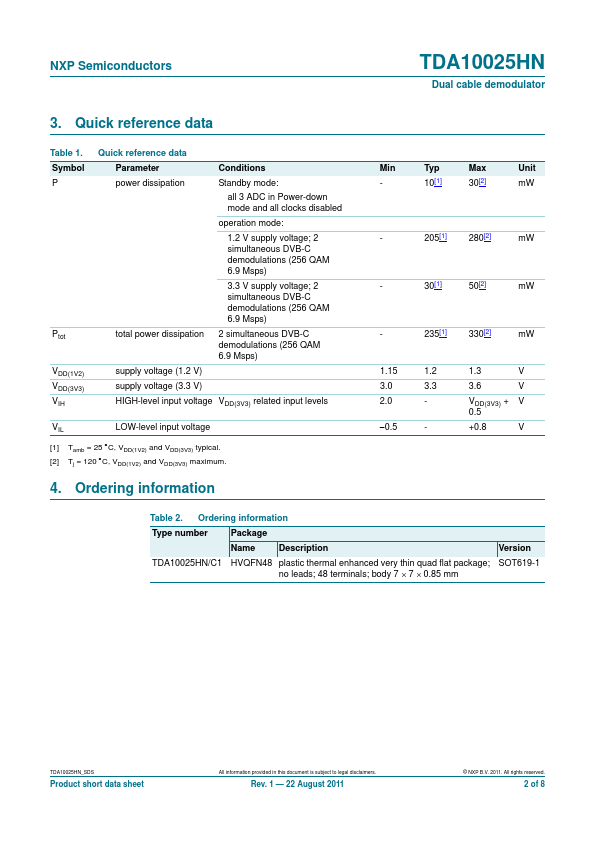

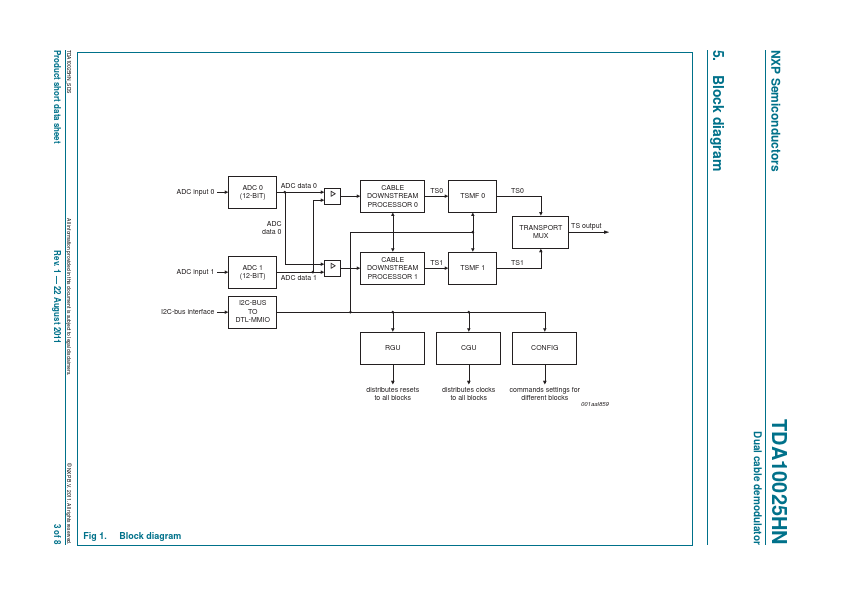

The TDA10025HN is a Dual Cable Downstream Processor. The Cable Downstream Processor (CDP) implements the physical interfaces and protocols required to provide the highest quality services of an in-band DOCSIS, EuroDOCSIS, DVB and OpenCable Set-Top Box (STB). The downstream signals are digitized by 12-bit ADC and passed to the Demod and Forward Error Correction (FEC) blocks, which do all the cable physical layer...

TDA10025HN Key Features

- QPSK, 16 QAM, 32 QAM, 64 QAM, 128 QAM and 256 QAM Demodulator

- ITU-T J83 Annex A, B and C FEC

- Transport Stream Multiplex Frame (TSMF) module for Annex C pliance

- Time interleaved parallel mode or serial mode for Transport Stream (TS) interface

- On chip PLL for crystal frequency multiplication (16 MHz external)

- Reuse of the tuner clock, saving one crystal

- Embedded 12-bit ADC

- 3.3 V and 1.2 V power supplies

- Low power < 235 mW for dual stream operation

- Small size package