PHX3055L

PHX3055L is PowerMOS transistor Logic level FET manufactured by NXP Semiconductors.

Philips Semiconductors

Preliminary specification

Power MOS transistor Logic level FET

GENERAL DESCRIPTION

N-channel enhancement mode logic level field-effect power transistor in a plastic full-pack envelope. The device Features high avalanche energy capability, stable blocking voltage, fast switching and high thermal cycling performance with low thermal resistance. Intended for use in Switched Mode Power Supplies (SMPS), motor control circuits and general purpose switching applications.

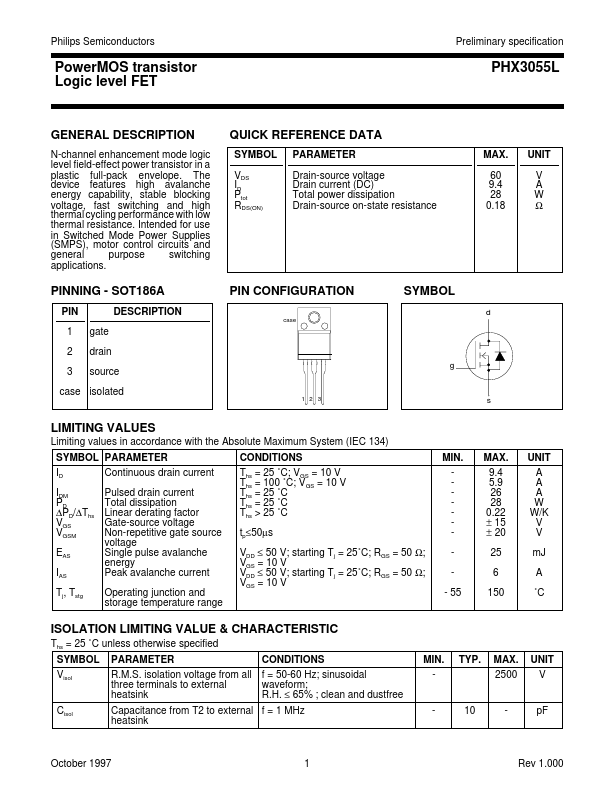

QUICK REFERENCE DATA

SYMBOL VDS ID Ptot RDS(ON) PARAMETER Drain-source voltage Drain current (DC) Total power dissipation Drain-source on-state resistance MAX. 60 9.4 28 0.18 UNIT V A W Ω

PINNING

- SOT186A

PIN 1 2 3 gate drain source DESCRIPTION

PIN CONFIGURATION case

SYMBOL d g case isolated

1 2 3 s

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134) SYMBOL PARAMETER ID IDM PD ∆PD/∆Ths VGS VGSM EAS IAS Tj, Tstg Continuous drain current Pulsed drain current Total dissipation Linear derating factor Gate-source voltage Non-repetitive gate source voltage Single pulse avalanche energy Peak avalanche current Operating junction and storage temperature range CONDITIONS Ths = 25 ˚C; VGS = 10 V Ths = 100 ˚C; VGS = 10 V Ths = 25 ˚C Ths = 25 ˚C Ths > 25 ˚C tp≤50µs VDD ≤ 50 V; starting Tj = 25˚C; RGS = 50 Ω; VGS = 10 V VDD ≤ 50 V; starting Tj = 25˚C; RGS = 50 Ω; VGS = 10 V MIN.

- 55 MAX. 9.4 5.9 26 28 0.22 ± 15 ± 20 25 6 150 UNIT A A A W W/K V V m J A ˚C

ISOLATION LIMITING VALUE & CHARACTERISTIC

Ths = 25 ˚C unless otherwise specified SYMBOL Visol PARAMETER R.M.S. isolation voltage from all three terminals to external heatsink CONDITIONS f = 50-60 Hz; sinusoidal waveform; R.H. ≤ 65% ; clean and dustfree MIN. TYP. MAX. 2500 UNIT V

Cisol

Capacitance from T2 to external f = 1 MHz heatsink

- 10

- p F

October 1997

Rev 1.000

Philips Semiconductors

Preliminary specification

Power MOS transistor Logic level FET

THERMAL...