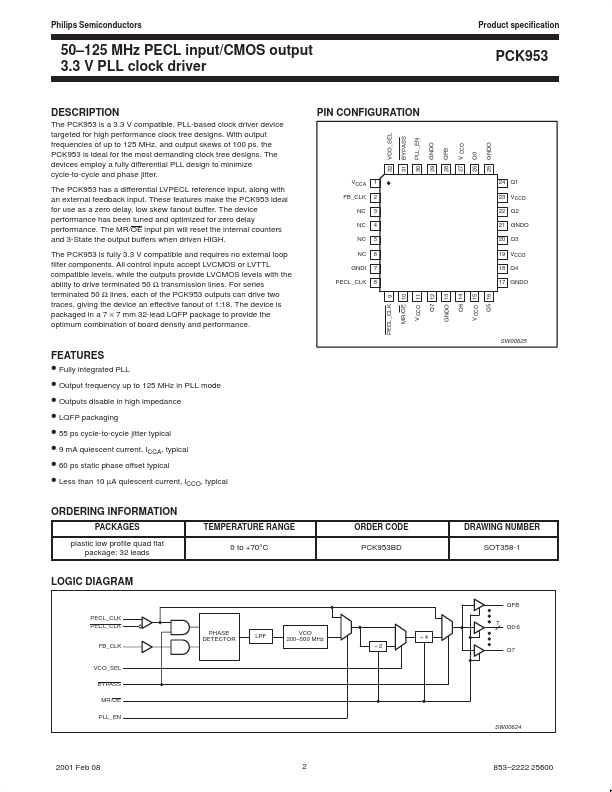

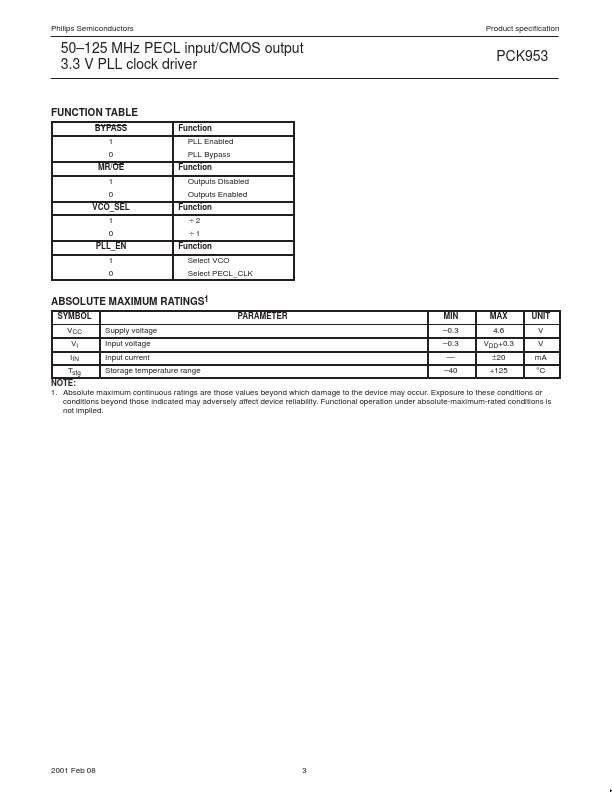

- Part: PCK953

- Description: 50-125 MHz PECL input/9 CMOS output 3.3 V PLL clock driver

- Manufacturer: NXP Semiconductors

- Size: 71.10 KB

Related NXP Semiconductors Datasheets

| Part Number | Description |

|---|---|

| PCK940L | Low voltage 1 : 18 clock distribution chip |

| PCK942C | Low voltage 1 : 18 clock distribution chip |

| PCK9446 | LVCMOS clock fan-out buffer |

| PCK9447 | LVCMOS clock fan-out buffer |

| PCK9448 | LVCMOS 1 : 12 clock fan-out buffer |