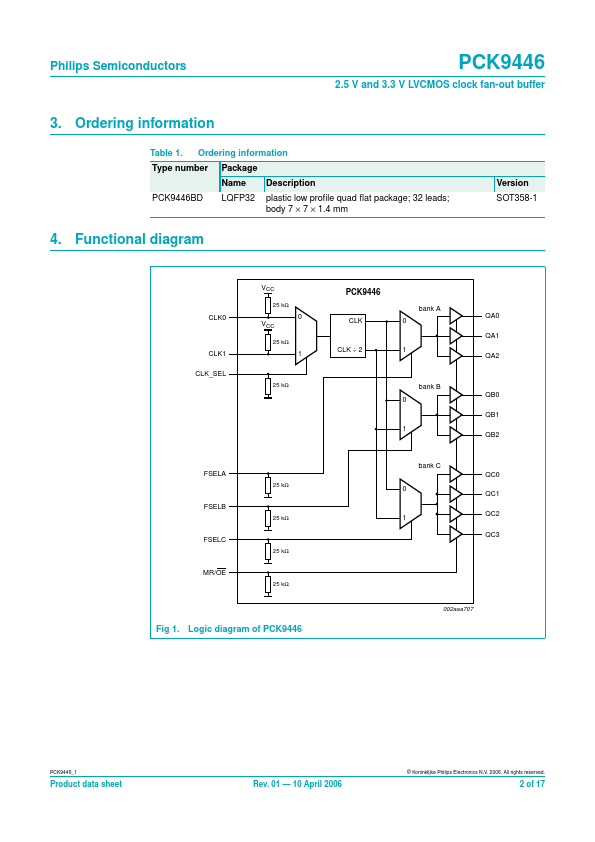

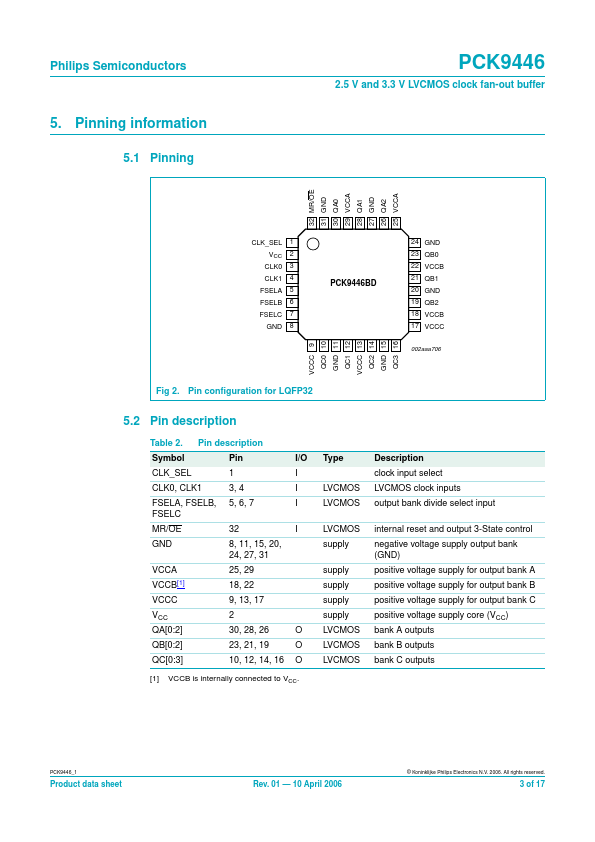

PCK9446 Overview

The PCK9446 is a 2.5 V and 3.3 V patible 1 : 10 clock distribution buffer designed for low-voltage mid-range to high-performance tele, networking and puting applications. Both 3.3 V, 2.5 V and dual supply voltages are supported for mixed-voltage applications.