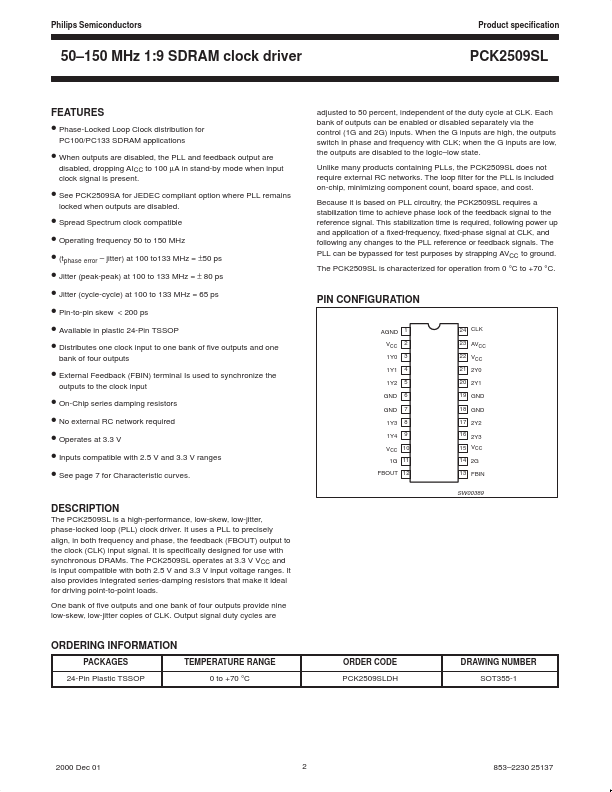

PCK2509SL Description

The PCK2509SL is a high-performance, low-skew, low-jitter, phase-locked loop (PLL) clock driver. It uses a PLL to precisely align, in both frequency and phase, the feedback (FBOUT) output to the clock (CLK) input signal. It is specifically designed for use with synchronous DRAMs.