P89C662 Key Features

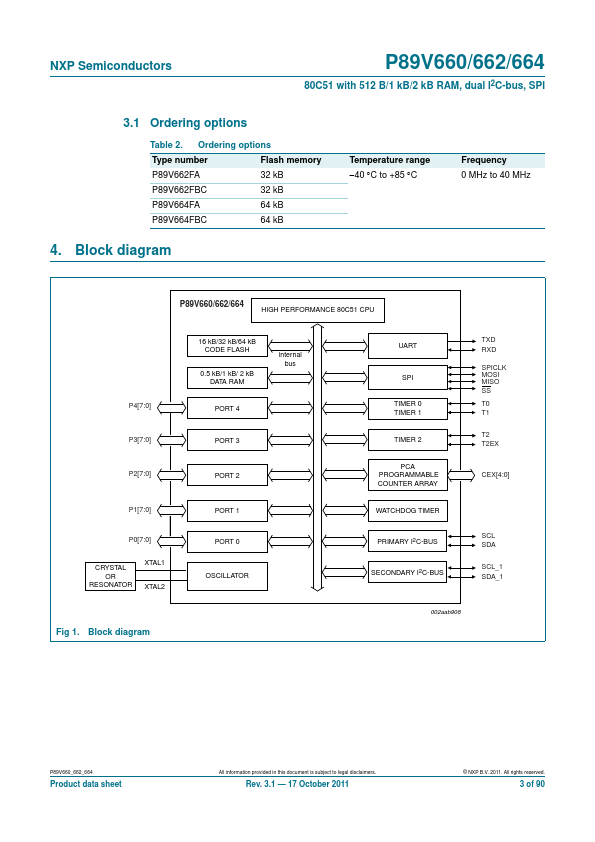

- Dual 100 kHz byte-wide I2C-bus interfaces

- 128-byte page erase for efficient use of code memory as non-volatile data storage

- 0 MHz to 40 MHz operating frequency in 12x mode, 20 MHz in 6x mode

- 16 kB/32 kB/64 kB of on-chip flash user code memory with ISP and IAP

- 512 B/1 kB/2 kB RAM

- SPI (Serial Peripheral Interface) and enhanced UART

- PCA (Programmable Counter Array) with PWM and Capture/pare functions

- Three 16-bit timers/counters

- Four 8-bit I/O ports, one 4-bit I/O port

- WatchDog Timer (WDT)