Datasheet Summary

PCA9665; PCA9665A

Fm+ parallel bus to I2C-bus controller

Rev. 4

- 29 September 2011

Product data sheet

1. General description

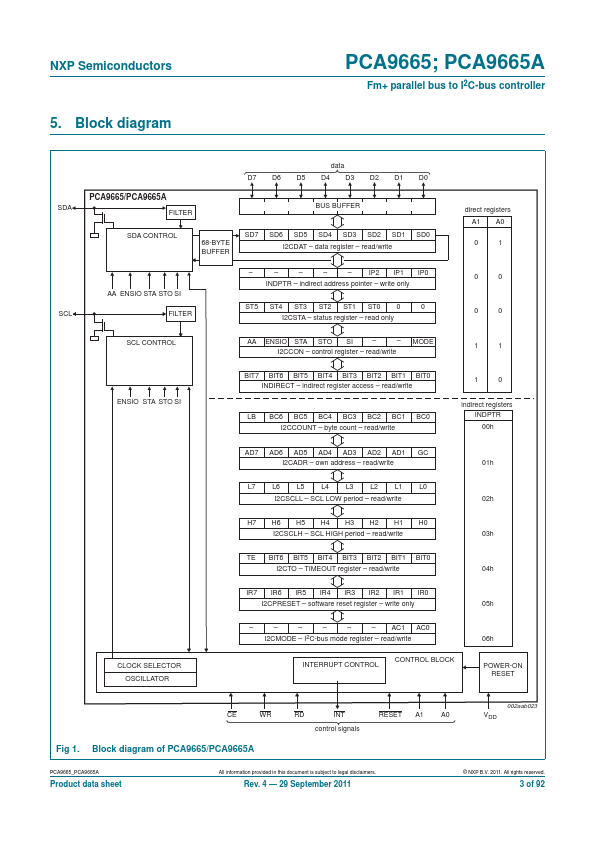

The PCA9665/PCA9665A serves as an interface between most standard parallel-bus microcontrollers/microprocessors and the serial I2C-bus and allows the parallel bus system to municate bidirectionally with the I2C-bus. The PCA9665/PCA9665A can operate as a master or a slave and can be a transmitter or receiver. munication with the I2C-bus is carried out on a Byte or Buffered mode using interrupt or polled handshake. The PCA9665/PCA9665A controls all the I2C-bus specific sequences, protocol, arbitration and timing with no external timing element required.

The...