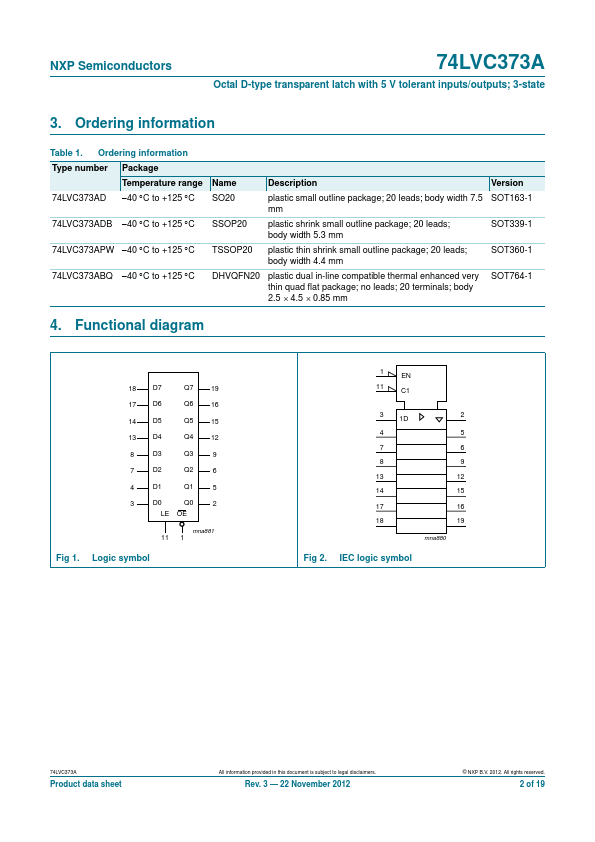

Datasheet Summary

Octal D-type transparent latch with 5 V tolerant inputs/outputs; 3-state

Rev. 3

- 22 November 2012

Product data sheet

1. General description

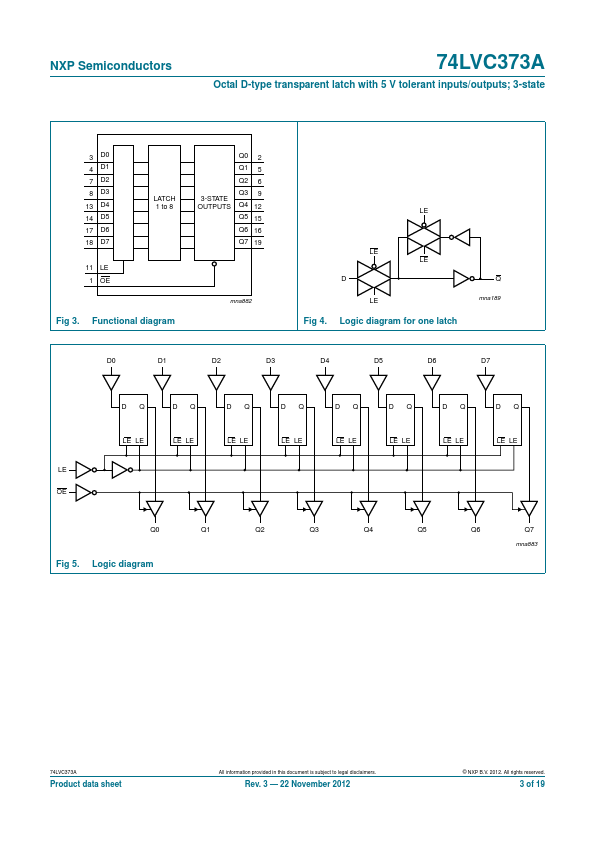

The 74LVC373A consists of eight D-type transparent latches, featuring separate D-type inputs for each latch and 3-state true outputs for bus-oriented applications. A latch enable input (pin LE) and an output enable input (pin OE) are mon to all internal latches.

When pin LE is HIGH, data at the D-inputs (pins D0 to D7) enters the latches. In this condition, the latches are transparent, that is, a latch output will change each time its corresponding D-input changes. When pin LE is LOW, the latches store the information that was present...