74HC4040

Overview

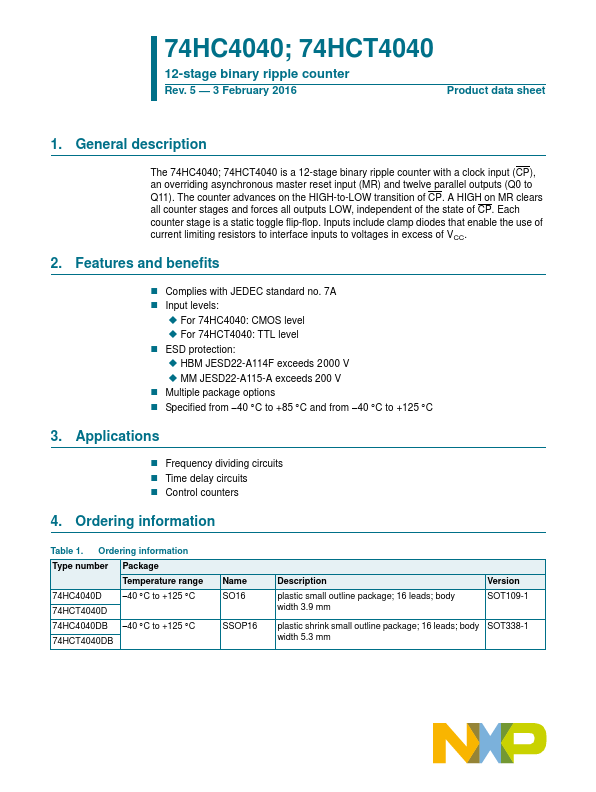

The 74HC4040; 74HCT4040 is a 12-stage binary ripple counter with a clock input (CP), an overriding asynchronous master reset input (MR) and twelve parallel outputs (Q0 to Q11). The counter advances on the HIGH-to-LOW transition of CP.

- Complies with JEDEC standard no. 7A

- Input levels:; For 74HC4040: CMOS level; For 74HCT4040: TTL level

- ESD protection:; HBM JESD22-A114F exceeds 2000 V; MM JESD22-A115-A exceeds 200 V

- Multiple package options

- Specified from -40 °C to +85 °C and from -40 °C to +125 °C