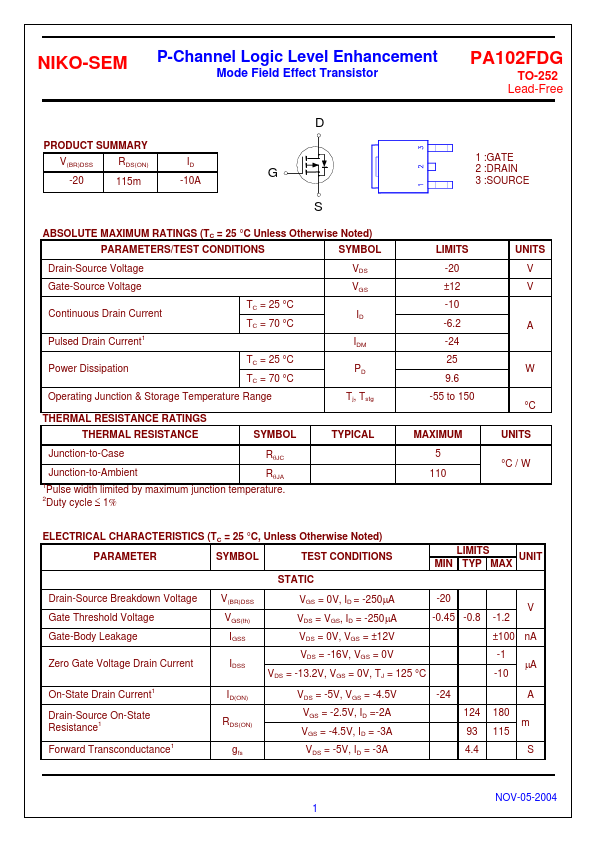

- Part: PA102FDG

- Description: P-Channel Logic Level Enhancement

- Manufacturer: NIKO-SEM

- Size: 261.06 KB

Datasheets by Manufacturer

- PA102FDG — VBsemi — P-Channel 30V MOSFET

- PA102FMG — UNIKC — P-Channel MOSFET

- PA102FMA — UNIKC — P-Channel MOSFET

- PA107DP — APEX — Power Operational Amplifiers

- PA1005.100NL — Pulse — TRANSFORMERS

- PA1005.020QNL — Pulse — SMT Current Sense Transformer

- PA1005.100QNL — Pulse — SMT Current Sense Transformer

- PA1066 — Tyco Electronics — 800-960MHz.Ultra Linear Amplifier

- PA10 — APEX — Power Operational Amplifier

- PA105 — OKAYA — NOISE SUPPRESSION CAPACITORS