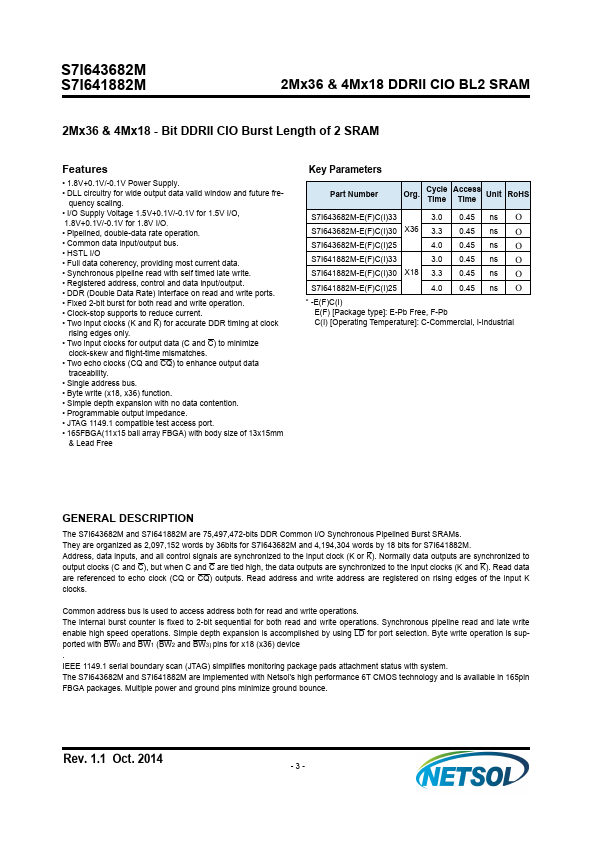

S7I643682M Overview

The S7I643682M and S7I641882M are 75,497,472-bits DDR.

S7I643682M Key Features

- 1.8V+0.1V/-0.1V Power Supply

- DLL circuitry for wide output data valid window and future fre

- I/O Supply Voltage 1.5V+0.1V/-0.1V for 1.5V I/O, 1.8V+0.1V/-0.1V for 1.8V I/O

- Pipelined, double-data rate operation

- mon data input/output bus

- HSTL I/O

- Full data coherency, providing most current data

- Synchronous pipeline read with self timed late write

- Registered address, control and data input/output

- DDR (Double Data Rate) Interface on read and write ports