UPD6379A

Overview

- Resistor string conversion method

- 0-point digital shift circuit

- × 4 oversampling Sampling frequency: 200 kHz MAX.

- Signal processing format for 2’s complement, MSB first, and backward justification data accommodated

- Left and right in-phase output

- High performance (at VDD = +5.0 V) S/N ratio: 100 dB TYP. Dynamic range: 96 dB TYP.

- Low-voltage models available

- Bipolar LR clock (LRCK)

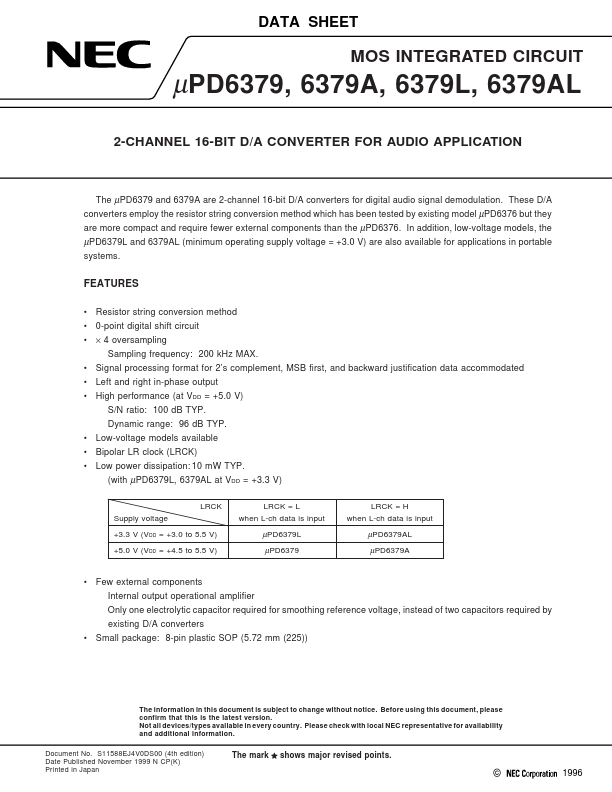

- Low power dissipation: 10 mW TYP. (with µPD6379L, 6379AL at VDD = +3.3 V) LRCK Supply voltage +3.3 V (VDD = +3.0 to 5.5 V) +5.0 V (VDD = +4.5 to 5.5 V) LRCK = L when L-ch data is input LRCK = H when L-ch data is input µPD6379L µPD6379 µPD6379AL µPD6379A

- Few external components Internal output operational amplifier Only one electrolytic capacitor required for smoothing reference voltage, instead of two capacitors required by existing D/A converters