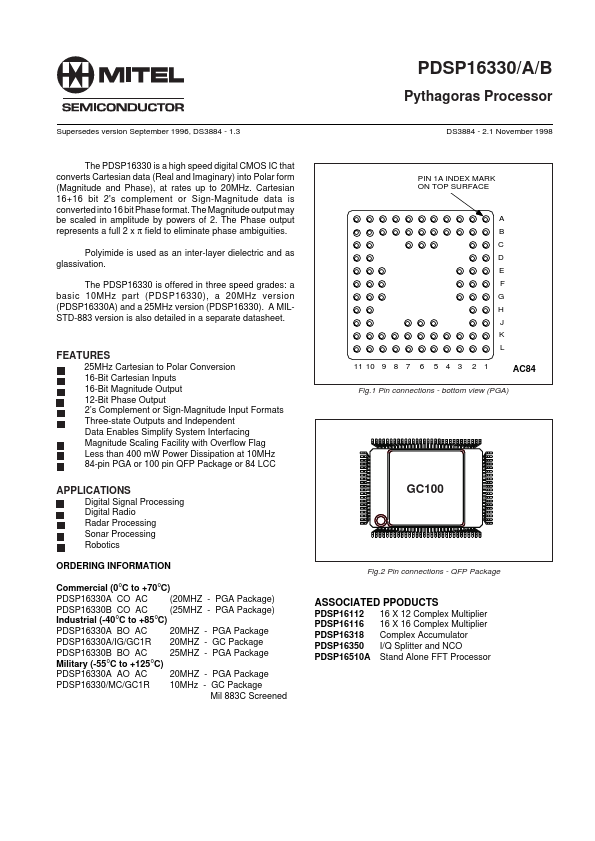

- Part: PDSP16330AAOAC

- Description: Pythagoras Processor

- Manufacturer: Mitel Networks Corporation

- Size: 173.17 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| PDSP16330A | Zarlink Semiconductor | Pythagoras Processor |

| PDSP16330 | Zarlink Semiconductor | Pythagoras Processor |

| PDSP16330MC | Zarlink Semiconductor | Pythagoras Processor |

| PDSP16330B | Zarlink Semiconductor | Pythagoras Processor |