Description

16-bit input for real X data 16-bit input for imaginary X data 16-bit input for real Y data 16-bit input for imaginary Y data 16-bit output for real P data 16-bit output for imaginary P data Clock; new data is loaded on rising edge of CLK Clock, enable X-port input register Clock, enable Y-port input register Conjugate X data Conjugate Y data Rounds the real and imaginary results Mode select (BFP/Normal) Start of BFP operations (see Note 1) End of pass (See Note 1) 3 MSBs from real part of A-word (See Note 1) 3 MSBs from imaginary part of A-word (See Note 1) Word tag from A-word Word tag from B-word/shift control (See Note 2) Word tag output (See Note 1) Shift control for A-word / overflow flag (See Note 2) Shift control for accumulator result (See Note 1) Global weighting register contents (See Note 1) Selects the desired output configuration Output enables 15V Supply (See Note 3) 0V Supply (See Note 3) CONX CONY ROUND MBFP SOBFP EOPSS Tie low Tie low Tie low Tie low Tie low Tie low AR15:1 3 Al15:1 3 WTA1:0 WTB1:0 WTOUT1:0 SFTA1:0 SFTR2:0 GWR4:0 OSEL1:0 OER, OEI VDD GND NOTES 1. Used only in BFP mode 2.

Key Features

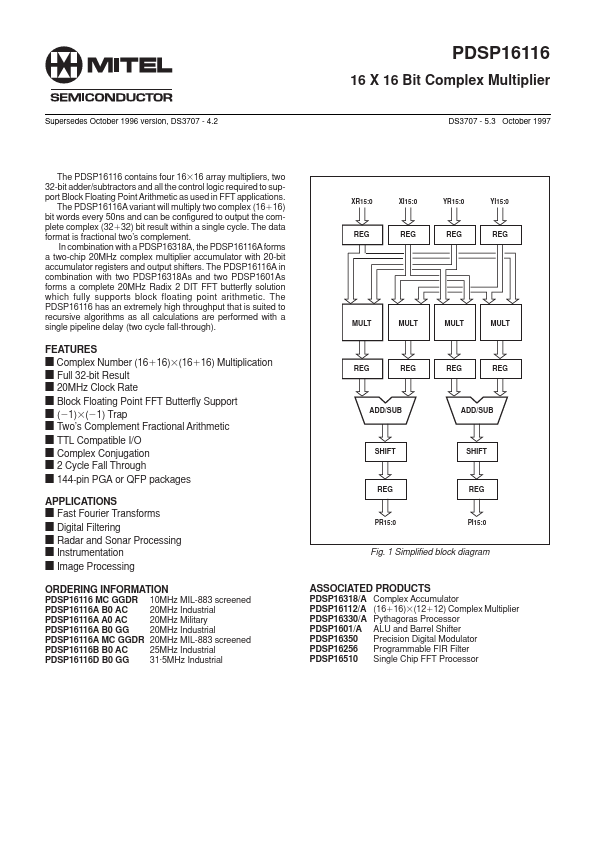

- 5MHz Industrial REG REG REG REG ADD/SUB ADD/SUB SHIFT SHIFT REG REG PR15:0 PI15:0 Fig. 1 Simplified block diagram