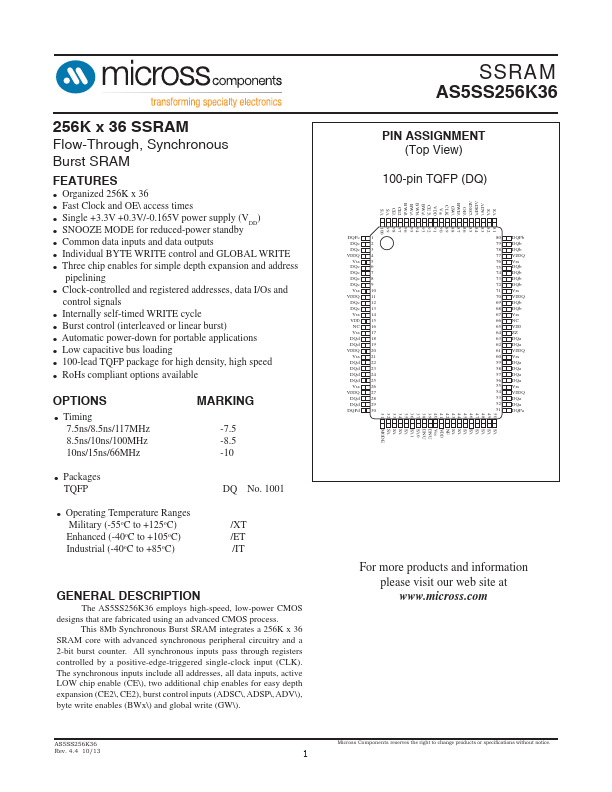

AS5SS256K36 Overview

Key Features

- Organized 256K x 36

- Fast Clock and OE\ access times

- Single +3.3V +0.3V/-0.165V power supply (VDD)

- SNOOZE MODE for reduced-power standby

- Common data inputs and data outputs

- Individual BYTE WRITE control and GLOBAL WRITE

- Three chip enables for simple depth expansion and address pipelining

- Clock-controlled and registered addresses, data I/Os and control signals

- Internally self-timed WRITE cycle

- Burst control (interleaved or linear burst)