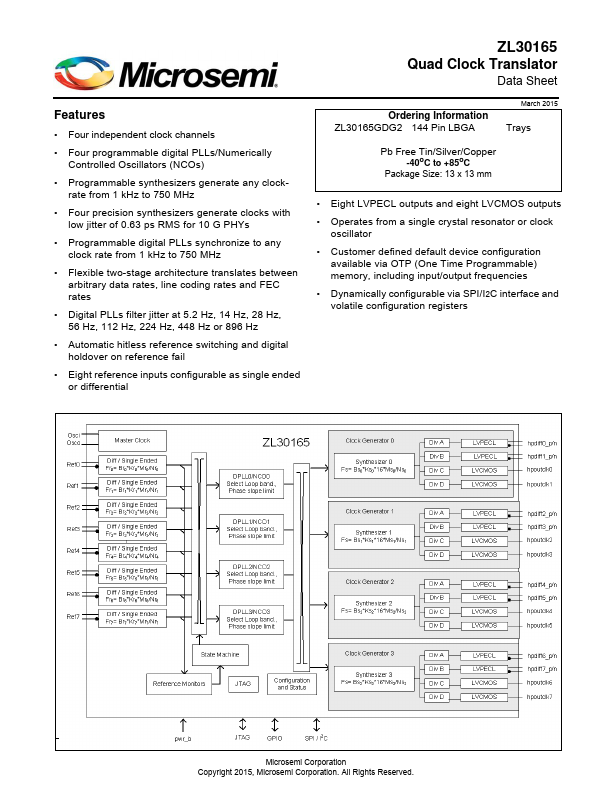

ZL30165 Description

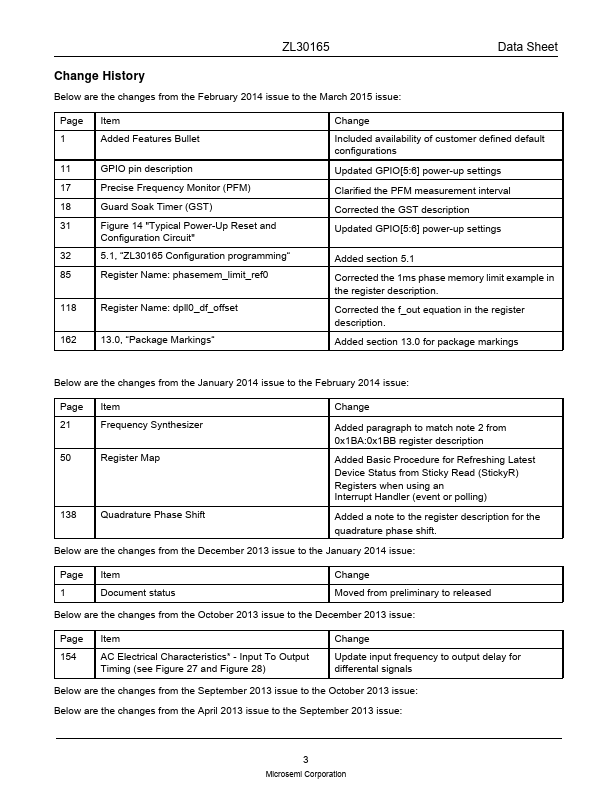

17 Precise Frequency Monitor (PFM) 18 Guard Soak Timer (GST) 31 Figure 14 "Typical Power-Up Reset and Configuration Circuit" 32 5.1, “ZL30165 Configuration programming“ 85 Register Name: phasemem_limit_ref0 118 Register Name: dpll0_df_offset 162 13.0, “Package Markings“ Change Included availability of customer defined default configurations Updated GPIO[5:6] power-up settings Clarified the PFM measurement interval...

ZL30165 Key Features

- Four independent clock channels

- Four programmable digital PLLs/Numerically Controlled Oscillators (NCOs)

- Programmable synthesizers generate any clockrate from 1 kHz to 750 MHz

- Four precision synthesizers generate clocks with low jitter of 0.63 ps RMS for 10 G PHYs

- Programmable digital PLLs synchronize to any clock rate from 1 kHz to 750 MHz

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates

- Digital PLLs filter jitter at 5.2 Hz, 14 Hz, 28 Hz, 56 Hz, 112 Hz, 224 Hz, 448 Hz or 896 Hz

- Automatic hitless reference switching and digital holdover on reference fail

- Eight reference inputs configurable as single ended or differential

- Eight LVPECL outputs and eight LVCMOS outputs