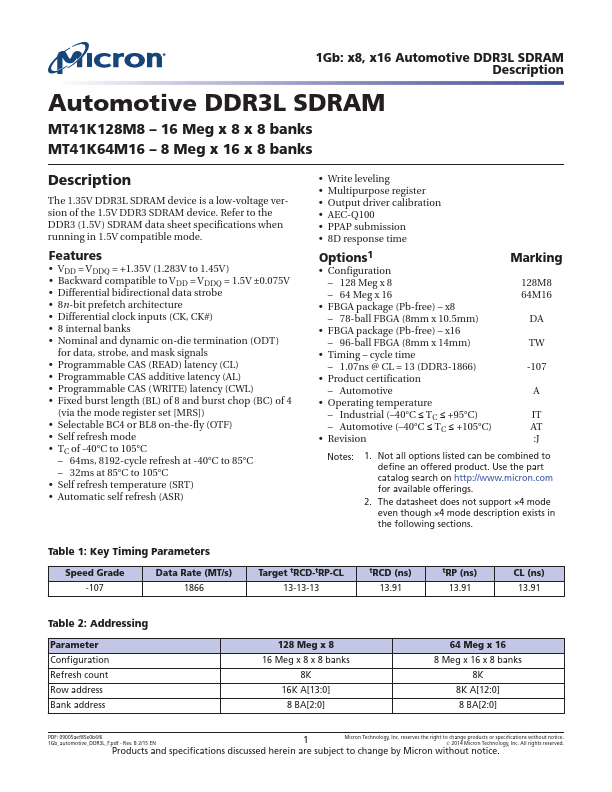

MT41K128M8 Overview

Key Specifications

Package: TFBGA

Mount Type: Surface Mount

Pins: 78

Operating Voltage: 1.35 V

Description

The 1.35V DDR3L SDRAM device is a low-voltage version of the 1.5V DDR3 SDRAM device. Refer to the DDR3 (1.5V) SDRAM data sheet specifications when running in 1.5V compatible mode.

Key Features

- VDD = VDDQ = +1.35V (1.283V to 1.45V)

- Backward compatible to VDD = VDDQ = 1.5V ±0.075V

- Differential bidirectional data strobe

- 8n-bit prefetch architecture

- Differential clock inputs (CK, CK#)