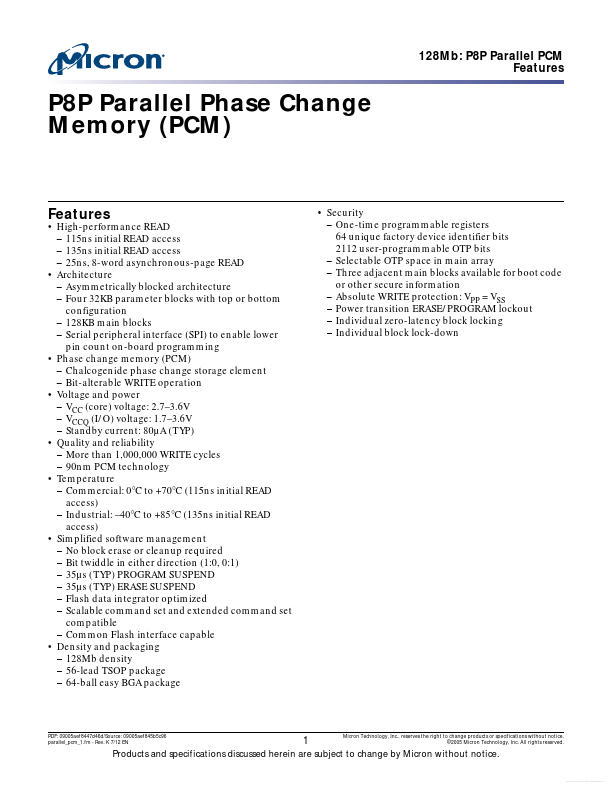

NP8P128AE3BSM60E

Overview

- High-performance READ - 115ns initial READ access - 135ns initial READ access - 25ns, 8-word asynchronous-page READ

- Architecture - Asymmetrically blocked architecture - Four 32KB parameter blocks with top or bottom configuration - 128KB main blocks - Serial peripheral interface (SPI) to enable lower pin count on-board programming

- Phase change memory (PCM) - Chalcogenide phase change storage element - Bit-alterable WRITE operation

- Voltage and power - VCC (core) voltage: 2.7-3.6V - VCCQ (I/O) voltage: 1.7-3.6V - Standby current: 80µA (TYP)

- Quality and reliability - More than 1,000,000 WRITE cycles - 90nm PCM technology

- Temperature - Commercial: 0°C to +70°C (115ns initial READ access) - Industrial: -40°C to +85°C (135ns initial READ access)

- Simplified software management - No block erase or cleanup required - Bit twiddle in either direction (1:0, 0:1) - 35µs (TYP) PROGRAM SUSPEND - 35µs (TYP) ERASE SUSPEND - Flash data integrator optimized - Scalable command set and extended command set compatible - Common Flash interface capable

- Density and packaging - 128Mb density - 56-lead TSOP package - 64-ball easy BGA package

- Security - One-time programmable registers 64 unique factory device identifier bits 2112 user-programmable OTP bits - Selectable OTP space in main array - Three adjacent main blocks available for boot code or other secure information - Absolute WRITE protection: VPP = VSS - Power transition ERASE/PROGRAM lockout - Individual zero-latency block locking - Individual block lock-down PDF: 09005aef8447d46d/Source: 09005aef845b5c96 parallel_pcm_ - Rev. K 7/12 EN 1 Micron Technology, Inc., reserves the right to change products or specifications without notice. ©2005 Micron Technology, Inc. All rights reserved. Products and specifications discussed herein are