PIC16F17126

PIC16F17126 is Microcontrollers manufactured by Microchip Technology.

PIC16F17126/46

PIC16F17126/46 Full-Featured 14/20-Pin Microcontrollers

Introduction

The PIC16F171 microcontroller family has a suite of analog peripherals that enables precision sensor applications. This product family is available from 8 to 44-pin packages in a memory range of 7 KB to 28 KB, with speeds up to 32 MHz. This product includes a low-noise Operational Amplifier (Op-Amp), a 12-bit differential Analog-to-Digital Converter with putation (ADCC), two 8-bit Digital-to-Analog Converters (DAC), up to four 16-bit Pulse-Width Modulation (PWM) peripherals, and many more waveform control and munication peripherals. This small form factor, feature-rich device is well suited for low-cost, energy-efficient analog sensor applications with higher resolution requirements.

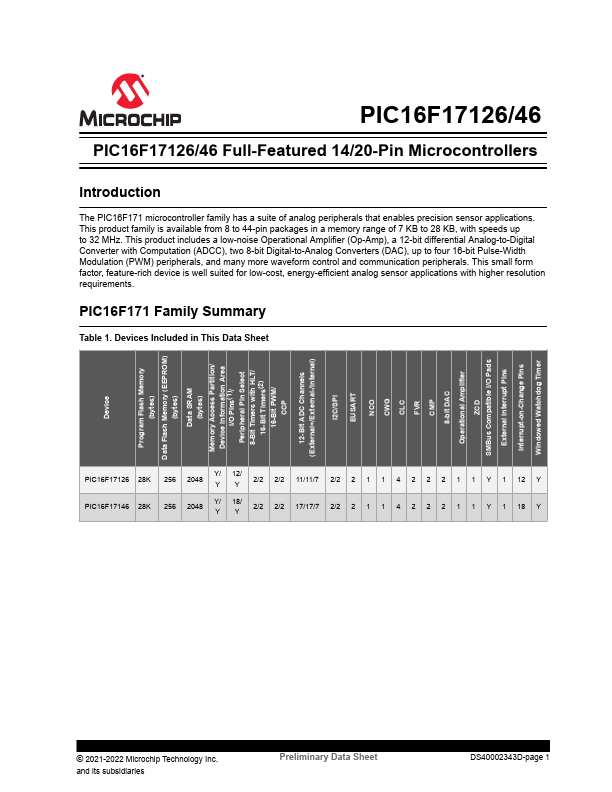

PIC16F171 Family Summary

Table 1. Devices Included in This Data Sheet

Device Program Flash Memory

(bytes) Data Flash Memory (EEPROM)

(bytes) Data SRAM

(bytes) Memory Access Partition/ Device Information Area

I/O Pins(1)/ Peripheral Pin Select 8-Bit Timers with HLT/

16-Bit Timers(2) 16-Bit PWM/ CCP

12-Bit ADC Channels (External+/External-/Internal)

I2C/SPI EUSART

NCO CWG CLC FVR CMP 8-bit DAC Operational Amplifier ZCD SMBus patible I/O Pads External Interrupt Pins Interrupt-on-Change Pins Windowed Watchdog Timer

PIC16F17126 28K PIC16F17146 28K

Y/ Y

12/ Y

2/2

2/2

11/11/7

2/2

Y/ Y

18/ Y

2/2

2/2

17/17/7

2/2

© 2021-2022 Microchip Technology Inc. and its subsidiaries

Preliminary Data...