MCP33121-10

Overview

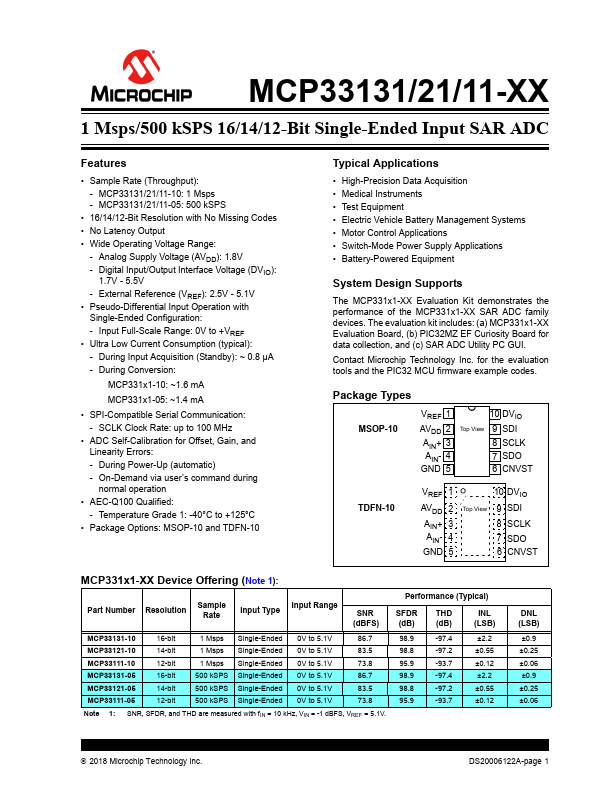

- Sample Rate (Throughput): - MCP33131/21/11-10: 1 Msps - MCP33131/21/11-05: 500 kSPS

- 16/14/12-Bit Resolution with No Missing Codes

- No Latency Output

- Wide Operating Voltage Range: - Analog Supply Voltage (AVDD): 1.8V - Digital Input/Output Interface Voltage (DVIO):

- 7V - 5.5V - External Reference (VREF): 2.5V - 5.1V

- Pseudo-Differential Input Operation with Single-Ended Configuration: - Input Full-Scale Range: 0V to +VREF

- Ultra Low Current Consumption (typical): - During Input Acquisition (Standby): ~ 0.8 µA - During Conversion: MCP331x1-10: ~1.6 mA MCP331x1-05: ~1.4 mA

- SPI-Compatible Serial Communication: - SCLK Clock Rate: up to 100 MHz

- ADC Self-Calibration for Offset, Gain, and Linearity Errors: - During Power-Up (automatic) - On-Demand via user’s command during normal operation

- AEC-Q100 Qualified: - Temperature Grade 1: -40°C to +125°C