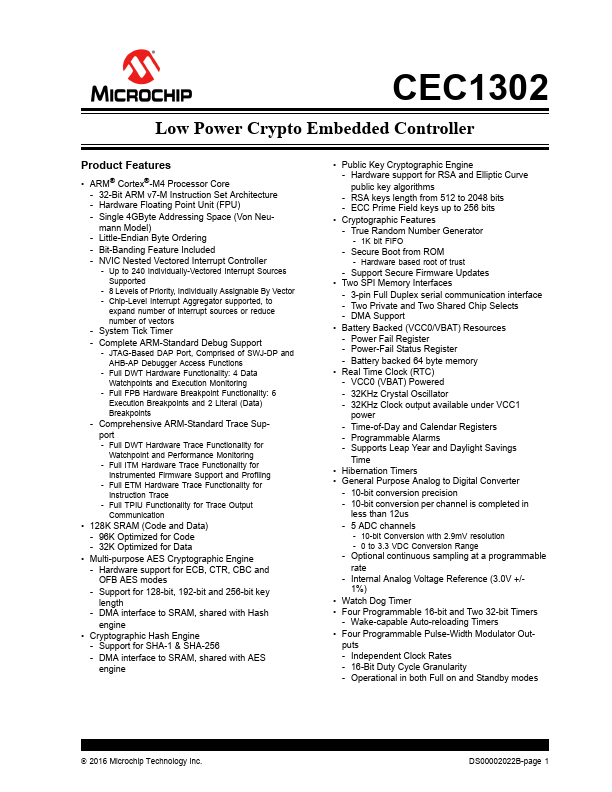

CEC1302

Overview

- ARM® Cortex®-M4 Processor Core - 32-Bit ARM v7-M Instruction Set Architecture - Hardware Floating Point Unit (FPU) - Single 4GByte Addressing Space (Von Neumann Model) - Little-Endian Byte Ordering - Bit-Banding Feature Included - NVIC Nested Vectored Interrupt Controller - Up to 240 Individually-Vectored Interrupt Sources Supported - 8 Levels of Priority, Individually Assignable By Vector - Chip-Level Interrupt Aggregator supported, to expand number of interrupt sources or reduce number of vectors - System Tick Timer - Complete ARM-Standard Debug Support - JTAG-Based DAP Port, Comprised of SWJ-DP and AHB-AP Debugger Access Functions - Full DWT Hardware Functionality: 4 Data Watchpoints and Execution Monitoring - Full FPB Hardware Breakpoint Functionality: 6 Execution Breakpoints and 2 Literal (Data) Breakpoints - Comprehensive ARM-Standard Trace Support - Full DWT Hardware Trace Functionality for Watchpoint and Performance Monitoring - Full ITM Hardware Trace Functionality for Instrumented Firmware Support and Profiling - Full ETM Hardware Trace Functionality for Instruction Trace - Full TPIU Functionality for Trace Output Communication

- 128K SRAM (Code and Data) - 96K Optimized for Code - 32K Optimized for Data

- Multi-purpose AES Cryptographic Engine - Hardware support for ECB, CTR, CBC and OFB AES modes - Support for 128-bit, 192-bit and 256-bit key length - DMA interface to SRAM, shared with Hash engine

- Cryptographic Hash Engine - Support for SHA-1 & SHA-256 - DMA interface to SRAM, shared with AES engine

- Public Key Cryptographic Engine - Hardware support for RSA and Elliptic Curve public key algorithms - RSA keys length from 512 to 2048 bits - ECC Prime Field keys up to 256 bits

- Cryptographic Features - True Random Number Generator - 1K bit FIFO - Secure Boot from ROM - Hardware based root of trust - Support Secure Firmware Updates

- Two SPI Memory Interfaces - 3-pin Full