PL500-17 Overview

Key Specifications

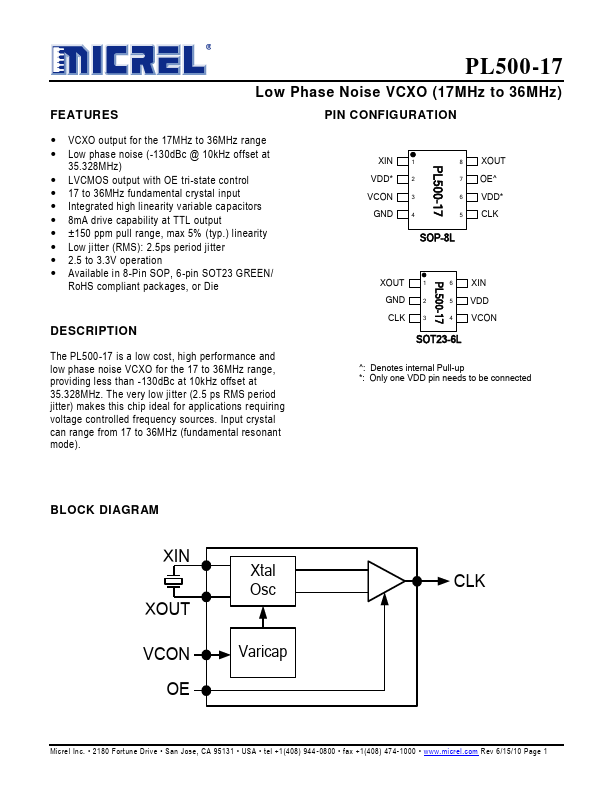

Package: SOIC

Mount Type: Surface Mount

Pins: 8

Max Frequency: 36 MHz

Description

The PL500-17 is a low cost, high performance and low phase noise VCXO for the 17 to 36MHz range, providing less than -130dBc at 10kHz offset at 35.328MHz. The very low jitter (2.5 ps RMS period jitter) makes this chip ideal for applications requiring voltage controlled frequency sources.