PL685-28 Overview

Key Specifications

Mount Type: Surface Mount

Max Frequency: 250 MHz

Max Operating Temp: 70 °C

Min Operating Temp: 0 °C

Description

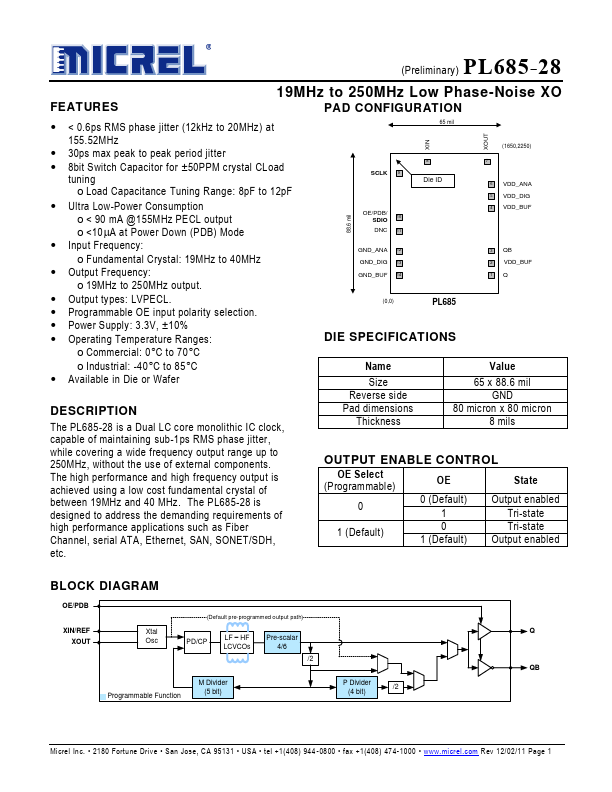

The PL685-28 is a Dual LC core monolithic IC clock, capable of maintaining sub-1ps RMS phase jitter, while covering a wide frequency output range up to 250MHz, without the use of external components. The high performance and high frequency output is achieved using a low cost fundamental crystal of between 19MHz and 40 MHz.