PL565-37

Overview

- Non-PLL frequency multiplication

- Input frequency from 30-62.5 MHz

- Output frequency from 120-250 MHz

- Low phase noise and jitter (equivalent to fundamental crystal at the output frequency)

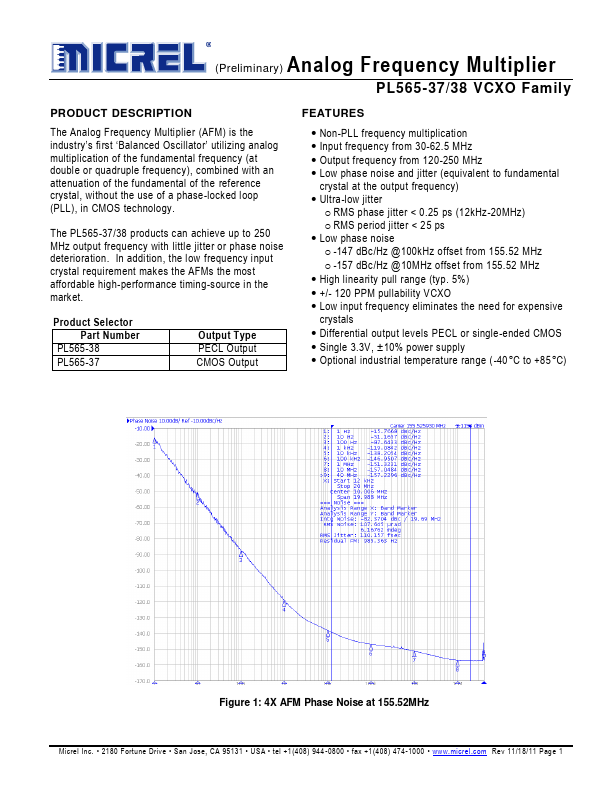

- Ultra-low jitter o RMS phase jitter < 0.25 ps (12kHz-20MHz) o RMS period jitter < 25 ps

- Low phase noise o -147 dBc/Hz @100kHz offset from 155.52 MHz o -157 dBc/Hz @10MHz offset from 155.52 MHz

- High linearity pull range (typ. 5%)

- +/- 120 PPM pullability VCXO

- Low input frequency eliminates the need for expensive crystals

- Differential output levels PECL or single-ended CMOS