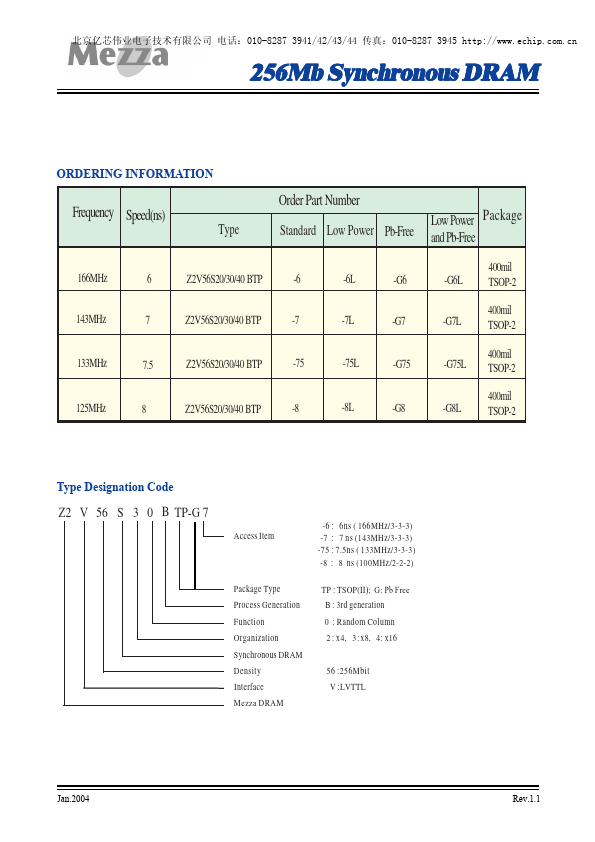

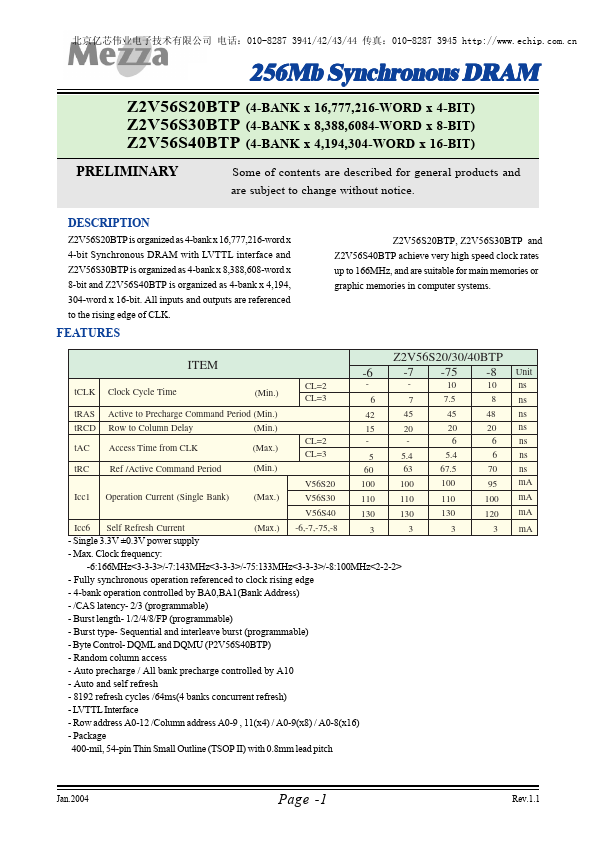

Z2V56S30BTP Overview

All inputs and outputs are referenced to the rising edge of CLK.

Z2V56S30BTP Key Features

- 6 -7 -75 -8

- Single 3.3V ±0.3V power supply

- Max. Clock frequency

- 6:166MHz<3-3-3>/-7:143MHz<3-3-3>/-75:133MHz<3-3-3>/-8:100MHz<2-2-2>

- Fully synch