MAX3639

Description

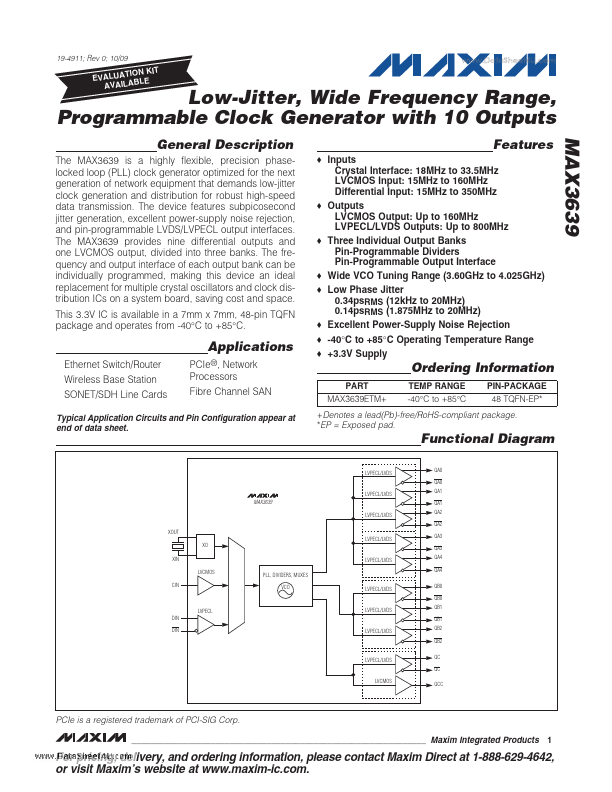

The MAX3639 is a highly flexible, precision phaselocked loop (PLL) clock generator optimized for the next generation of network equipment that demands low-jitter clock generation and distribution for robust high-speed data transmission. The device features subpicosecond jitter generation, excellent power-supply noise rejection, and pin-programmable LVDS/LVPECL output interfaces.