MAX3638

MAX3638 is Programmable Clock Generator manufactured by Maxim Integrated.

19-4910; Rev 0; 10/09

..

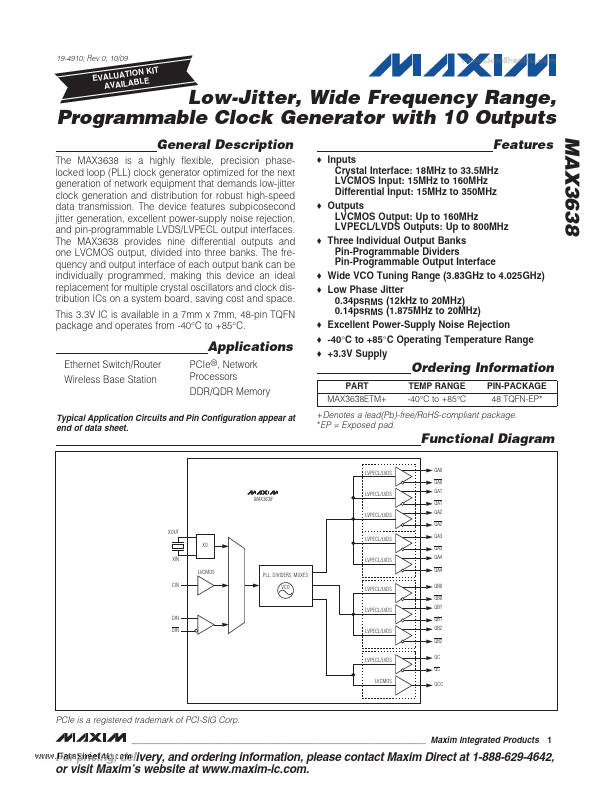

Low-Jitter, Wide Frequency Range, Programmable Clock Generator with 10 Outputs

General Description

The MAX3638 is a highly flexible, precision phaselocked loop (PLL) clock generator optimized for the next generation of network equipment that demands low-jitter clock generation and distribution for robust high-speed data transmission. The device Features subpicosecond jitter generation, excellent power-supply noise rejection, and pin-programmable LVDS/LVPECL output interfaces. The MAX3638 provides nine differential outputs and one LVCMOS output, divided into three banks. The frequency and output interface of each output bank can be individually...