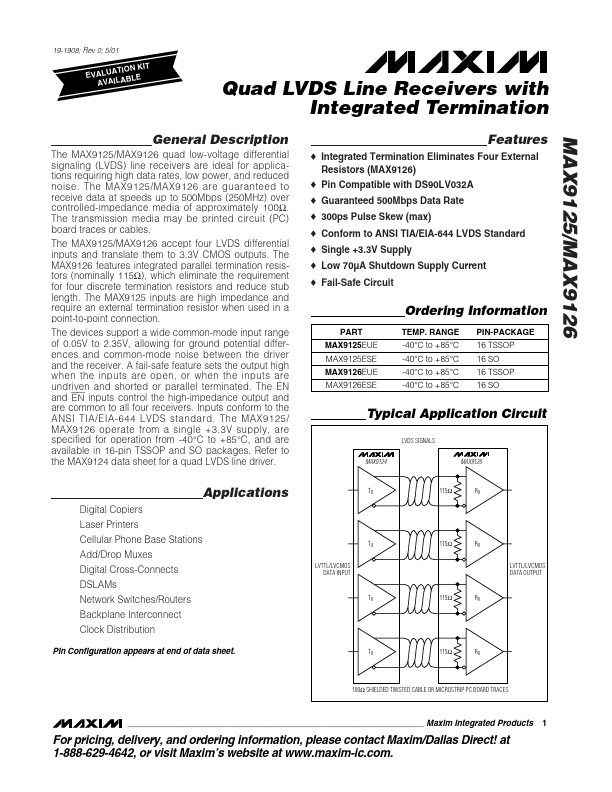

MAX9126 Description

The MAX9125/MAX9126 quad low-voltage differential signaling (LVDS) line receivers are ideal for applications requiring high data rates, low power, and reduced noise. The MAX9125/MAX9126 are guaranteed to receive data at speeds up to 500Mbps (250MHz) over controlled-impedance media of approximately 100Ω. The transmission media may be printed circuit (PC) board traces or cables.