MN101C67D Description

AM1 (MN101) Series AM1 (MN101) Series The AM1 Series of 8-bit microputers is the realization of developments in C programming. Because of the 8-bit architecture, which allows half-byte instruction sets and offers other advantages, assembler ROM code size can be reduced. They are pact and consume little power, but.

MN101C67D Key Features

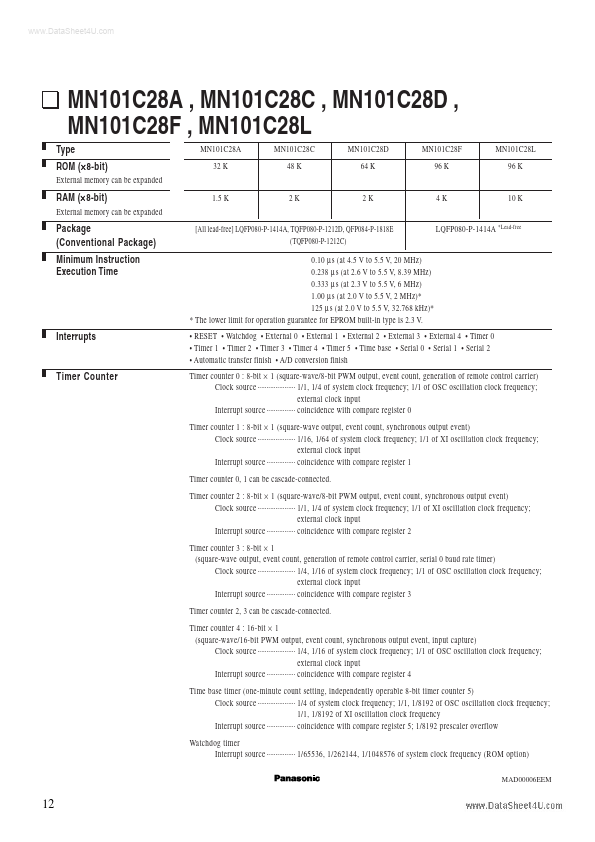

- The lower limit for operation guarantee for EPROM built-in type is 2.3 V

- Watchdog

- External 0

- External 1

- External 2

- External 3

- External 4

- Timer 0

- Timer 1

- Timer 2

MN101C67D Applications

- The lower limit for operation guarantee for EPROM built-in type is 2.3 V