ISPCLOCK5600A

Description

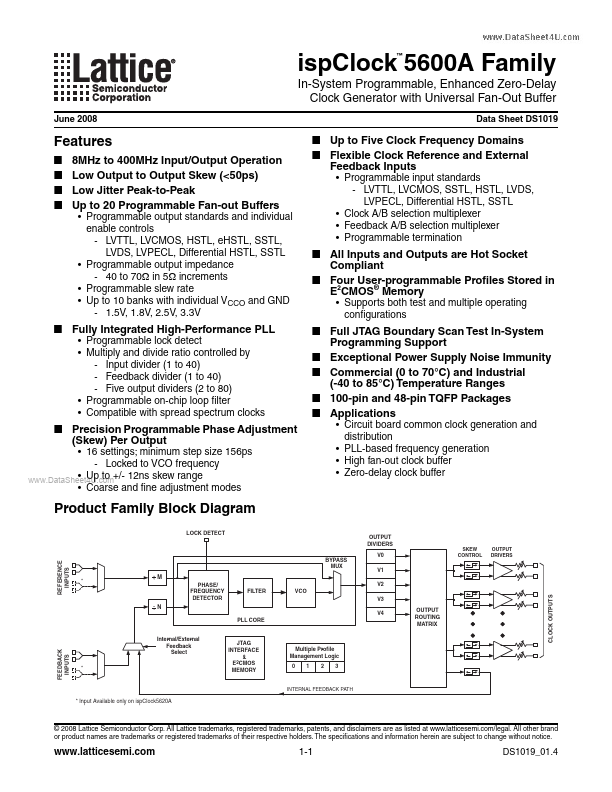

and Overview The ispClock5610A and ispClock5620A are in-system-programmable high-fanout enhanced zero delay clock generators designed for use in high performance munications and puting applications. The ispClock5610A provides up to 10 single-ended or five differential clock outputs, while the ispClock5620A provides up to 20 singleended or 10 differential clock outputs.

Key Features

- 8MHz to 400MHz Input/Output Operation Low Output to Output Skew (<50ps) Low Jitter Peak-to-Peak Up to 20 Programmable Fan-out Buffers

- Programmable output standards and individual enable controls

- LVTTL, LVCMOS, HSTL, eHSTL, SSTL, LVDS, LVPECL, Differential HSTL, SSTL

- Programmable output impedance

- 40 to 70Ω in 5Ω increments

- Programmable slew rate

- Up to 10 banks with individual VCCO and GND

- 1.5V, 1.8V, 2.5V, 3.3V

- Up to Five Clock Frequency Domains

- Flexible Clock Reference and External Feedback Inputs