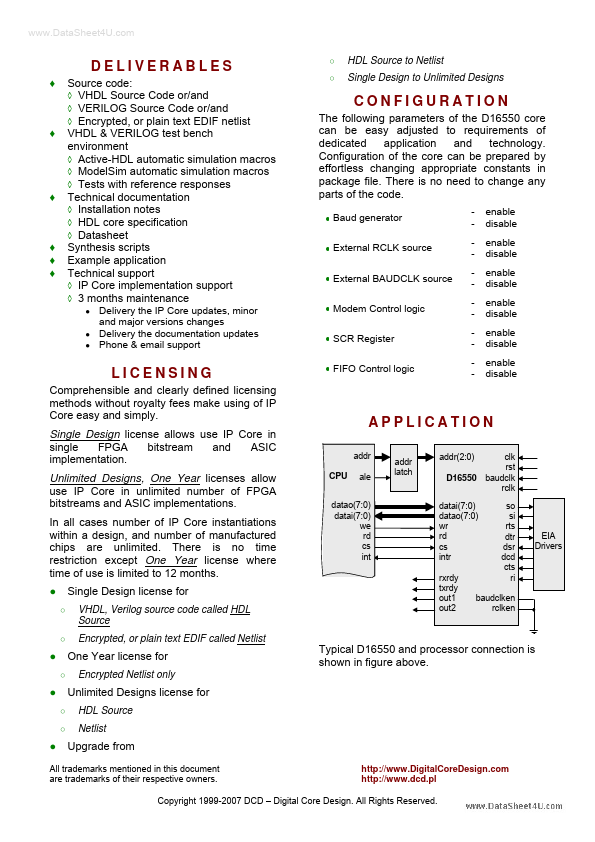

Datasheet Summary

..

Configurable UART with FIFO ver 2.11

OVERVIEW

The D16550 is a soft Core of a Universal Asynchronous Receiver/Transmitter (UART) functionally identical to the TL16C550A. The D16550 allows serial transmission in two modes: UART mode and FIFO mode. In FIFO mode internal FIFOs are activated allowing 16 bytes (plus 3 bits of error data per byte in the RCVR FIFO) to be stored in both receive and transmit directions. D16550 performs serial-toparallel conversion on data characters received from a peripheral device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the plete status of the UART at any time during...