RED3000 Overview

Description

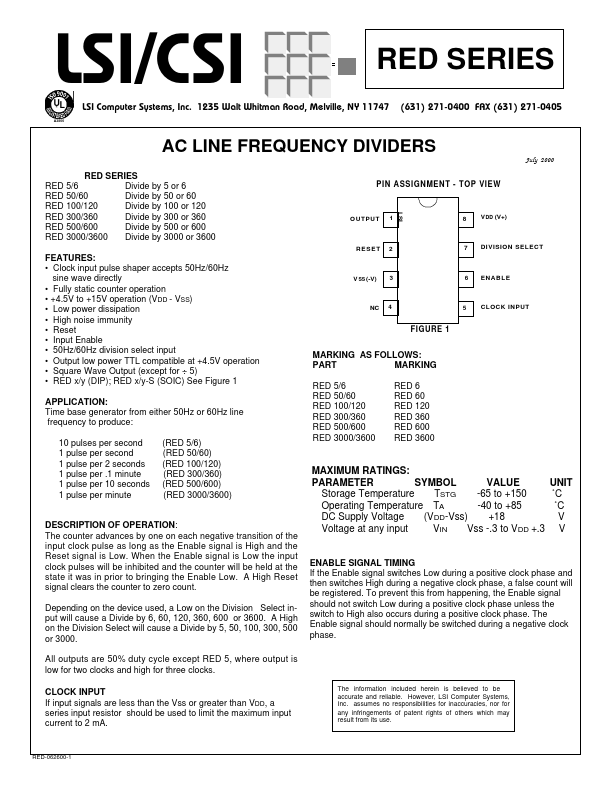

OF OPERATION: The counter advances by one on each negative transition of the input clock pulse as long as the Enable signal is High and the Reset signal is Low. When the Enable signal is Low the input clock pulses will be inhibited and the counter will be held at the state it was in prior to bringing the Enable Low.

Key Features

- Clock input pulse shaper accepts 50Hz/60Hz sine wave directly

- Fully static counter operation

- +4.5V to +15V operation (VDD

- Low power dissipation

- High noise immunity