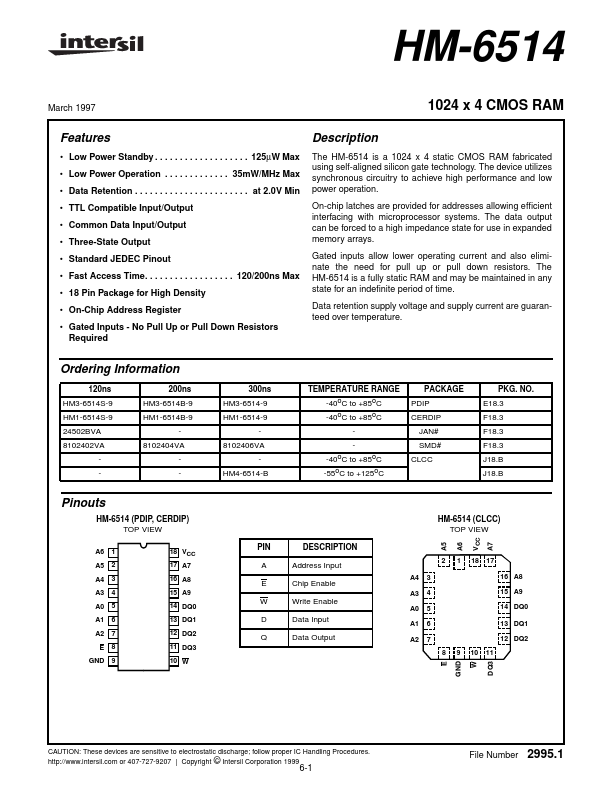

HM3-6514-9 Overview

Description

The HM-6514 is a 1024 x 4 static CMOS RAM fabricated using self-aligned silicon gate technology. The device utilizes synchronous circuitry to achieve high performance and low power operation.

Key Features

- Low Power Standby . . . . . . . . . . . . . . . . . . . 125µW Max

- Low Power Operation . . . . . . . . . . . . . 35mW/MHz Max

- Data Retention . . . . . . . . . . . . . . . . . . . . . . . at 2.0V Min

- TTL Compatible Input/Output

- Common Data Input/Output

- Three-State Output

- Standard JEDEC Pinout

- Fast Access Time. . . . . . . . . . . . . . . . . . 120/200ns Max

- 18 Pin Package for High Density

- On-Chip Address Register